Hi Stu,

The document is accurate. As far as R Series cards go, only the 781xR and 783xR can access the Local Bus lines, which do not include the lines that I mentioned in my previous post (PXI_TRIG lines). I did not recommend these because of the fact that Ben said in his first post that he is communicating between a 7813R and a 7852R. Although the 7813R can communicate on the Local Bus, the 7852R cannot, and therefore must use the PXI_TRIG lines if communication across the backplane is desired.

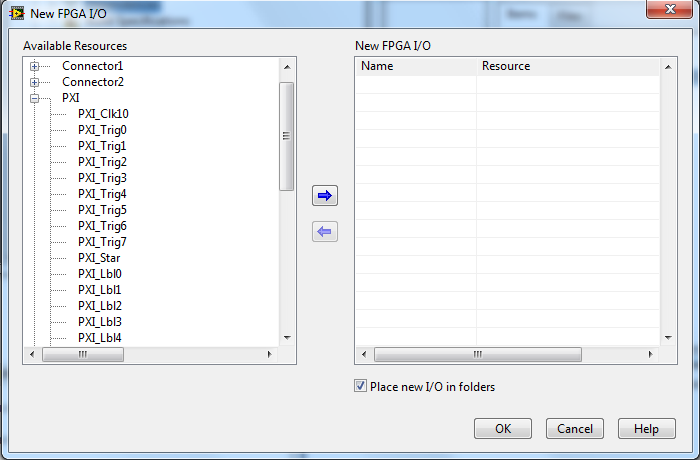

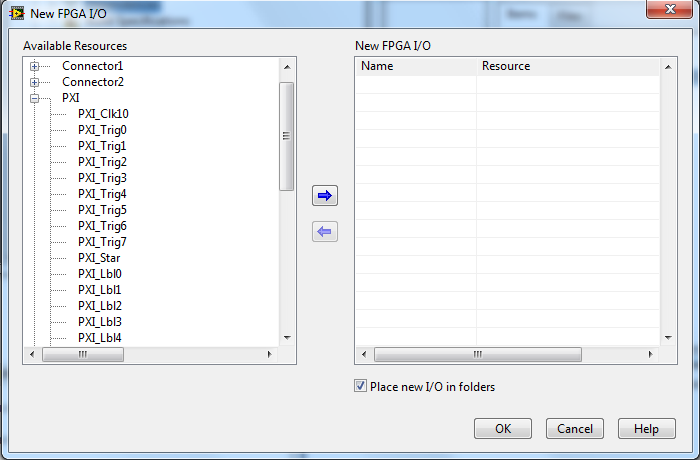

If you were to create a project with an existing or simulated 781xR or 783xR card, you will notice in the New FPGA I/O dialog that there is a PXI grouping, and underneath that you will see all available PXI lines to read/write. For these cards which have access to the Local Bus, you will not only see PXI_Clk10, PXI_Star, and all of the PXI_Trig lines, but also local bus lines, labeled PXI_Lbl0 – PXI_Lbl12 and PXILbr_0 – PXI_lbr12.

The Lbl and Lbr names stand for “local bus left” and “local bus right”. These buses are basically used to communicate information with adjacent slots to the left and right of the module. Once you have added the FPGA I/O to your project, you can drag & drop the corresponding I/O nodes into your project just like you would with any other FPGA I/O.

If you are interested in learning more, check out Accessing PXI Local Bus Lines Using R-Series Cards.

Chris_G

Sr Test Engineer

Medtronic, Inc.