- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

Getting flow sensor frequency using FPGA and using DMA FIFO from target to host. Not getting correct number of samples in output TDMS file and unable to get correct number of pulses from flow sensor.

03-14-2019 05:20 PM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

Hey guys, I have been trying to get a flow sensor reading by counting the number of pulses given out by the flow meter.

I use NI 9205 analog input module in differential mode with 9.5 to 10 Volts and 11 mA excitation from a voltage generator, with a Compact Rio 9036. The frequency output from the flow sensor is 40Hz to 1200 Hz. The sampling frequency is 2 KHz(1/(20,000 ticks*25ns)) where 25ns is the FPGA clock rate.

Using DMA FIFO, the data is acquired by the rt loop-

Problems;

1. instead of getting 120,000 samples (2khz*60sec), I get only 24,000. why?

2. I counted the pulses in matlab but I get only around 900 pulses in a minute. I guess this is obvious from point 1?

I have attached the VI's, the TDMS files with readings for 1min with constant flow of around 1.05 litres per minute, second VI where flow is reduced from 1.05 litres per minute to a lesser one and then to 1.05 lpm again

and the flow meter specs

Can someone please advise me what to do here? As I've been breaking my head over this for 10 days. I'm new to labview and data acquisition.

03-15-2019 02:42 AM - edited 03-15-2019 03:04 AM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

Hi ashwin,

next time please attach the full project: without your lvproj file those FPGA/RT VIs are pretty senseless…

Why do you need to use SGL data in your FPGA VI? Why not stick with FXP and integer data?

Why are there several charts in the FPGA VI? The FPGA is not able to show a frontpanel on a monitor!

Why is there an additional wait function inside the TWL of your RT VI? (Palm face!)

Why do you need a TWL at all when the loop needs to wait on a certain number of samples in the FPGA FIFO?

Why do you need to reshape a 1D array into a 2D array of just one row???

03-15-2019 04:13 AM - edited 03-15-2019 04:21 AM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

lv project - the google drive link to the project

Thank you GerdW for the reply, I was hoping you'd answer as I just don't know what is going wrong.

1) I was using FXP initially but for no particular reason was trying out what sgl does.

2) Yes I am aware of that, its because the frequency is too high to show on a monitor, right? But as i wasn't getting results I was trying out everything.

3)The thing is I think I am missing some data, so I put a wait function to see what happens when I change it.

4) I was initially taking 2 to 3 inputs, that is why I was reshaping.

As you see I'm still new to labview and learning most of the stuff by seeing what happens after trying.

I tried to attach the project but I get an error "The attachment's flow_fpga.lvproj content type (application/octet-stream) does not match its file extension and has been removed"

03-15-2019 04:21 AM - edited 03-15-2019 04:40 AM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

Hi ashwinsn,

I tried to attach the project but I get an error "The attachment's flow_fpga.lvproj content type (application/octet-stream) does not match its file extension and has been removed"

Put everything inside a ZIP file.

Added bonus: only one upload for you and only one download for us!

I was using FXP initially but for no particular reason was trying out what sgl does.

SGL uses way more FPGA resources than FXP. In the way you use it you don't get any added benefit…

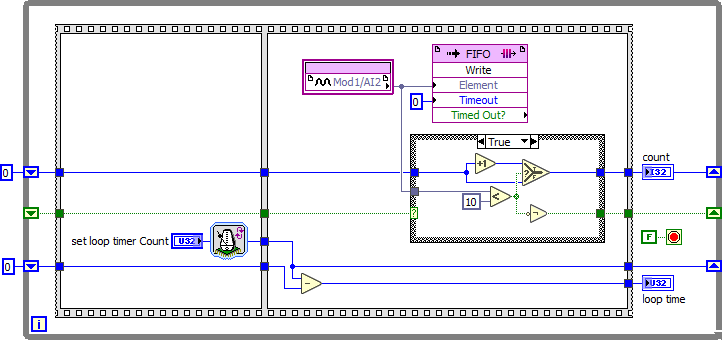

Cleanup your FPGA to something like this:

Also change the datatype of the FIFO to use the very same as your NI9205 module (±,20,5)…

03-15-2019 04:23 AM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

I've already added the project to the previous reply , if you don't mind.

03-15-2019 04:47 AM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

Hi ashwinsn,

I used that link in your previous message, but in general it is preferred to find every needed file in a ZIP, attached to your message in this forum. (Sometimes there can be problems to access 3rd party websites!)

03-18-2019 04:28 AM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

Dear GerdW, can you help me understand what happens to the signal when it goes through the NI 9205 ?

As the flow sensor gives out push pull type pulse outputs. It is connected to the NI 9205 which has an ADC therefore shouldn’t I be getting a digital signal in labview through the compact Rio ? What is happening exactly ?

Also, if I’ve set the sample rate at 2 KHz, I should be getting 2000*60 sample points in the TDMS file right ?

03-18-2019 04:46 AM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

Hi ash,

As the flow sensor gives out push pull type pulse outputs. It is connected to the NI 9205 which has an ADC therefore shouldn’t I be getting a digital signal in labview through the compact Rio ?

The NI9205 is an AI module, reading voltage signals.

You get analog values (as FXP in the FPGA)…

Also, if I’ve set the sample rate at 2 KHz, I should be getting 2000*60 sample points in the TDMS file right ?

You should get 2000 sample per second, in case you really sample at 2kHz sample rate.

03-18-2019 05:28 AM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

@GerdW wrote:

Hi ashwin,

next time please attach the full project: without your lvproj file those FPGA/RT VIs are pretty senseless…

Why do you need to use SGL data in your FPGA VI? Why not stick with FXP and integer data?

Why are there several charts in the FPGA VI? The FPGA is not able to show a frontpanel on a monitor!

Why is there an additional wait function inside the TWL of your RT VI? (Palm face!)

Why do you need a TWL at all when the loop needs to wait on a certain number of samples in the FPGA FIFO?

Why do you need to reshape a 1D array into a 2D array of just one row???

In relation to the bolded part: Having a chart on the FP of a FPGA VI can be immensely useful when debugging (and connecting to the VI in interactive mode can help show some possible problems). I do this a lot, but I also tend to have the Chart on a VI which calls the actual FPGA VI as a sub-VI (and plotting a GBL to the chart) allowing me to test with chart but deploy without. So this point would have been low on my personal list of things wrong.

Just my 2c.

03-21-2019 10:31 AM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

Hi GerdW,

I tried what you said and then I tried a lot of other things. But I still cannot get the reading from the flow sensor.

I have attached the project. I set the fpga loop to 20,000 ticks, so that is 2khz, I'm reading 1000 elements from FIFO every 500ms in the RT loop.

I'm using a shared variable rt fifo to seperate the producer and consumer tasks.

I'm getting the flow as 52 pulses per second..even after I switch off the pump the reading doesn't change.

I really do not know what I should do. been at this for weeks.