- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

Getting flow sensor frequency using FPGA and using DMA FIFO from target to host. Not getting correct number of samples in output TDMS file and unable to get correct number of pulses from flow sensor.

03-21-2019 10:42 AM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

Also, when I look at the waveform cart in rt consumer, the voltage seems to reduce and then increase, which is not supposed to happen because the voltage should remain constant..

03-21-2019 11:44 AM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

Hi ash,

when I look at the waveform cart in rt consumer, the voltage seems to reduce and then increase, which is not supposed to happen because the voltage should remain constant..

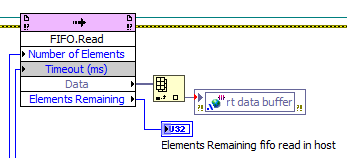

You are doing some funny things with your FIFO data in the RT VI:

- pick just one (the first) sample from the read FIFO data

- transfer that singe sample to the other loop

- building a 1D array with this single sample

- reshaping that 1D array of 1 element to a 2D array of 1×1 element for saving

- why are there 3 more empty strings in the array constant defining the channel names for the TDMS file?

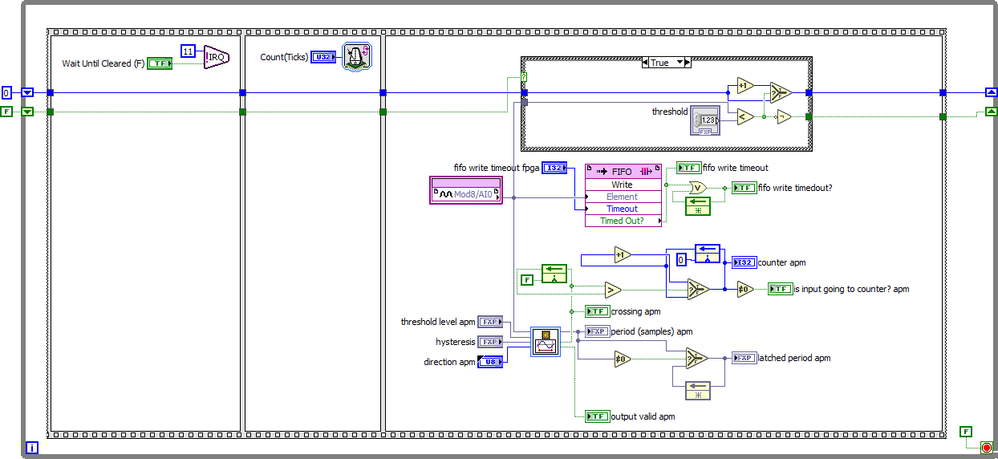

On the FPGA VI:

You really should not use SGL data in the FPGA. Why not stick with I32 and boolean data?

Why do you let the FPGA wait for an IRQ with each iteration?

All the output values are buffered in shift registers or feedback node: ofcourse the will stay the same when the FPGA doesn't iterate or gets new pulses…

03-22-2019 05:31 AM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

Hi GerdW, I have taken the IRQ out of the loop.

"All the output values are buffered in shift registers or feedback node: ofcourse the will stay the same when the FPGA doesn't iterate or gets new pulses…"

What do you mean by this? But the FPGA iterates and keeps getting values when I run the RT vi.

The analog period measurement counter gets updated in RT.

"You are doing some funny things with your FIFO data in the RT VI:

- pick just one (the first) sample from the read FIFO data

- transfer that singe sample to the other loop

- building a 1D array with this single sample

- reshaping that 1D array of 1 element to a 2D array of 1×1 element for saving

- why are there 3 more empty strings in the array constant defining the channel names for the TDMS file?"

Is these question or suggestions? 😮 ..if i pick one sample from read FIFO each time, will the FIFO not overflow as a result of getting filled from fpga fifo write?

Yes I've changed the data types in FPGA.. I am new to labview and did not quite know the properties of each datatype

03-22-2019 05:38 AM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

Hi ash,

What do you mean by this? But the FPGA iterates and keeps getting values when I run the RT vi.

The analog period measurement counter gets updated in RT.

Before the last message you wrote:

even after I switch off the pump the reading doesn't change.

So I guess you still get (unreasonable) values from FPGA even though there is no massflow anymore?

Is these question or suggestions?

This is a suggestion to think about what you are doing and what you need…

Why do you put samples at kHz rate into the FIFO, when you only use one single of sample per data block?

Yes I've changed the data types in FPGA.. I am new to labview and did not quite know the properties of each datatype

You should try to learn LabVIEW first - with a simpler project than FPGA+RT involved…

03-22-2019 06:18 AM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

So I guess you still get (unreasonable) values from FPGA even though there is no massflow anymore?

yes.

Why do you put samples at kHz rate into the FIFO, when you only use one single of sample per data block?

I'm trying to read 2000 samples in one second into the fifo and then read a higher number of samples per loop from the FIFO in Host.

What do you mean by one single sample per data block?

You should try to learn LabVIEW first - with a simpler project than FPGA+RT involved…

I'm learning by doing and have already got the basics by doing the basic programs as you said

03-22-2019 09:03 AM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

Hi ash,

What do you mean by one single sample per data block?

This one:

You are reading an array of samples from your FPGA - and then you pick just the first sample of that array.

Unfortunately you didn't set any default values in all your controls, so I cannot guess how many samples you are reading from the FIFO or how long the loop waits for next iteration…

Do you really need to configure the FIFO with each iteration of your RT host loop???

03-25-2019 06:54 AM - edited 03-25-2019 06:55 AM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

I have set controls for FIFO read so that I can change the values while troubleshooting. I do not really require to configure the fifo for each iteration.

I tried seeing the flow sensor output on an Oscilloscope, but just got a constant DC voltage.

But when I see the output from the ni 9205 in the scan interface mode, I get kind of pulses which gradually reduce in amplitude and then come back to the initial amplitude.

Any ideas what is going on?

Do I need to use any resistors in the circuit?

03-25-2019 07:36 AM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

Hi ash,

reading that pulse pattern seems wrong: when your scope doesn't show those pulses then most probably they don't exist.

How did you wire your NI9205? Is there any shielding? Are there (switching) power supplies nearby?

03-25-2019 08:10 AM - edited 03-25-2019 08:14 AM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

Hi GerdW,

What do you mean by how did you wire the 9205? Its connected to the cRIO and the flowsensor wires are the input to it.

There is a power supply "EA Elektro-Automatik EA-3048B". I use it to power the flow sensor.

And the power supply for the cRIO is nearby. There is no shielding to the wires going in the 9205.

But that aside, the scope itself shows a dc voltage.

Could this problem be because of the power supply?

03-25-2019 08:41 AM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

Hi ash,

What do you mean by how did you wire the 9205?

Which wire is connected to which pin. Every wire counts…

Even better: attach a schematic of your circuit!

There is a power supply "EA Elektro-Automatik EA-3048B". … And the power supply for the cRIO is nearby. There is no shielding to the wires going in the 9205.

When there are power supplies "nearby" shielding becomes interesting…