-

Analysis & Computation

305 -

Development & API

2 -

Development Tools

1 -

Execution & Performance

1,027 -

Feed management

1 -

HW Connectivity

115 -

Installation & Upgrade

267 -

Networking Communications

183 -

Package creation

1 -

Package distribution

1 -

Third party integration & APIs

289 -

UI & Usability

5,456 -

VeriStand

1

- New 3,057

- Under Consideration 4

- In Development 4

- In Beta 0

- Declined 2,640

- Duplicate 714

- Completed 336

- Already Implemented 114

- Archived 0

- Subscribe to RSS Feed

- Mark as New

- Mark as Read

- Bookmark

- Subscribe

- Printer Friendly Page

- Report to a Moderator

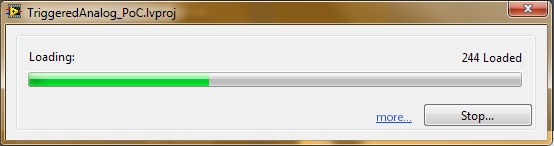

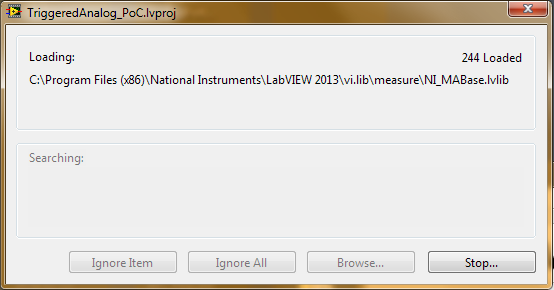

Progress bar when loading dependencies

When you launch a LabVIEW Project or Top Level VI with many Sub VIs, it can take some time while LabVIEW searches and loads all dependencies. This is especially true when working with large RF applications. Better CPUs and SSDs make the loading faster, but the loading time is still fairly long for most PCs.

I propose that the 'Loading Dialog', which normally shows 'Ignore Item', 'Ignore All', 'Browse' and 'Cancel' is augmented to have a Progress Bar. Seasoned LabVIEW users are familiar with the process of loading files, however, new users will find the progress bar less daunting than a dialog box with lots of text flashing on their screen with complex words like 'Loading', 'Searching' or 'Mass Compiling'.

I would like to take a cue from the Windows 8 Copy/Paste dialog box, where a standard progress bar is shown, unless you request to see more information.

Proposed New User Experience:

To get back to Classic User Experience: click 'more...', or if a dependency cannot be found:

Kudos if you like the idea.

George T.

Senior Applications Engineer

National Instruments UK and Ireland

You must be a registered user to add a comment. If you've already registered, sign in. Otherwise, register and sign in.