- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

VeriStand FPGA XML Builder Node Feedback

05-20-2014 05:16 PM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

Welcome to the VeriStand FPGA XML Builder node feedback forum. Please use this forum for any questions or feedback you may have regarding this add-on.

05-21-2014 07:04 PM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

I'm just getting started with this tool; thanks for putting it together. It may be outside the intent of the tool, but the Input terminals don't seem to re-adapt to new datatypes after they've first been wired. I haven't found a way to re-configure the terminal within the configuration dialog box either. For example, drop a new FPGA XML.xnode, wire a Boolean to Input_1, then try to wire any other datatype to Input_1. The wire breaks. I tried replacing the FPGA XML.xnode, and the first terminal "re-adapted", but the node condensed and disconnected all my other IO. Expanding the new node didn't re-connect the wires. I don't think this will be too big of a deal because the interface probably won't change much, if at all. However, is there an easy way to re-adapt to new data types, or should I start over with a new node? Thanks! -Steve K

05-21-2014 07:10 PM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

Please consider scraping the bitfile name from the project instead of defaulting to "My Bitfile". And I'd like a pony. A pink pony that does my laundry. Thanks! -Steve K

05-22-2014 10:02 AM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

Hi Steve,

Been a while! Hope everything is well with you!

I saw the tool demoed earlier this week, and I believe you can reconfigure inputs/outputs by right-clicking the node and selecting a new type. I agree that it would be cool if it automatically adapted to new types though

05-22-2014 11:08 AM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

Hey Steve,

Thanks for the feedback, you raise some good points. With regards to changing the type of an input, you follow the same process for setting the type of an output. If you left click on the input row, a menu list will appear allowing you to specify the data type of that row. This can be changed even after wiring up an input and is discussed further in step 10 of the "Instructions for Use" document attached on the Add-On's page.

As for automatically re-adapting to input data types, we had considered this. However, we designed the node to differentiate channels based on their signal type (and corresponding symbol that is displayed in VeriStand); so AI, AO, DI, DO, PWM In and PWM Out. Since a AI can be of the U64 type, and a PWM In is also of the U64 type, we had to choose a default between the two. So any U64 that's wired up will default to AI >> U64. (Also discussed in step 10 of the "Instructions for Use" guide). The user can then change this to be PWM In to get the proper channel type. If we constantly checked for a difference in data type we'd have to introduce some corner cases to handle AI >> U64 and AI >> PWM In specially. Since the data type of inputs shouldn't be changing often after first wired, we made the decision to only allow for manual re-configuration. The only exception here is Fixed Point inputs. If you wire up a Fixed Point input of type <+,16,8> then change it to be a Fixed Point of <+,32,12>, the node does read and accept the new values for sign, word length, and integer word length.

As for pulling the bitfile name, I agree that using the bitfile name from the project would be a better default and have added that to our features list for future development. We certainly appreciate the feedback, keep it coming!

--Ryan_S

05-22-2014 01:53 PM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

Hi Devin, Thanks man, I hope you're well as well (and well as a well well). Yes, you can reconfigure the terminals, but it's the left mouse button, "Configure each terminal (white row) by left clicking on the row..." in step 10 of the PDF. Hi Ryan, Thanks for explaining the decision behind the design. I agree with the auto-adapt decision. Thanks for considering the bitfile name and re-explaining the way to change the terminal types. Feel free to hit me with RTFM any time I should 😉 -Steve K

05-22-2014 07:19 PM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

Hey Steve,

No problem, and definitely keep the feedback coming. We hope to continue advancing the tool, as needed, so all feedback and suggestions are welcome.

--Ryan_S

05-29-2014 12:21 PM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

I'm having good results with the node.

- It would be nice to have the "Remove Input" and "Add Input" context menu choices, similar to property nodes and cluster operations. The behavior could be to delete/add the input/output but keep all adjacent inputs/outputs wired. I'm not sure if XNodes support this behavior.

- It would be nice for the node configuration tree control in the node configuration dialog box to support highlighting multiple items. The behavior could be to move multiple items into different categories at once.

Thanks for listening! -Steve K

05-30-2014 12:49 PM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

Hey Steve,

I'm glad to hear the node is working well for you and hopefully it saves to you time when creating a new FPGA personality to use with VeriStand. I appreciate the additional feedback; both of those items are already on our list of improvements to make, they just didn't get there before release. Thanks!

05-30-2014 12:59 PM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

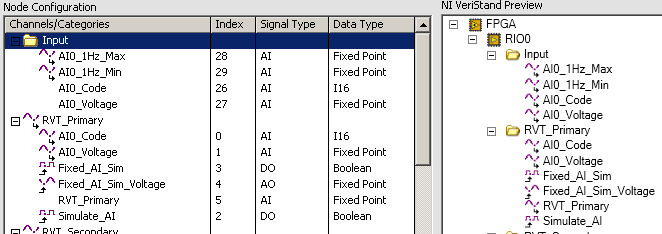

There may be an issue where adding nodes after the XML has been generated cause the Node Configuration tree control icons to become incorrect. The NI VeriStand Preview icons remain correct. I haven't scrutinized the XML yet to isolate it to a display glitch.

RVT_Primary and RVT_Secondary are categories, as shown in the VeriStand preview, but they're showing up as AI channels. Also note a few of the other glyphs are blank. Thanks! -Steve K