- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

Introducing delay before start next...

05-03-2013 06:51 AM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

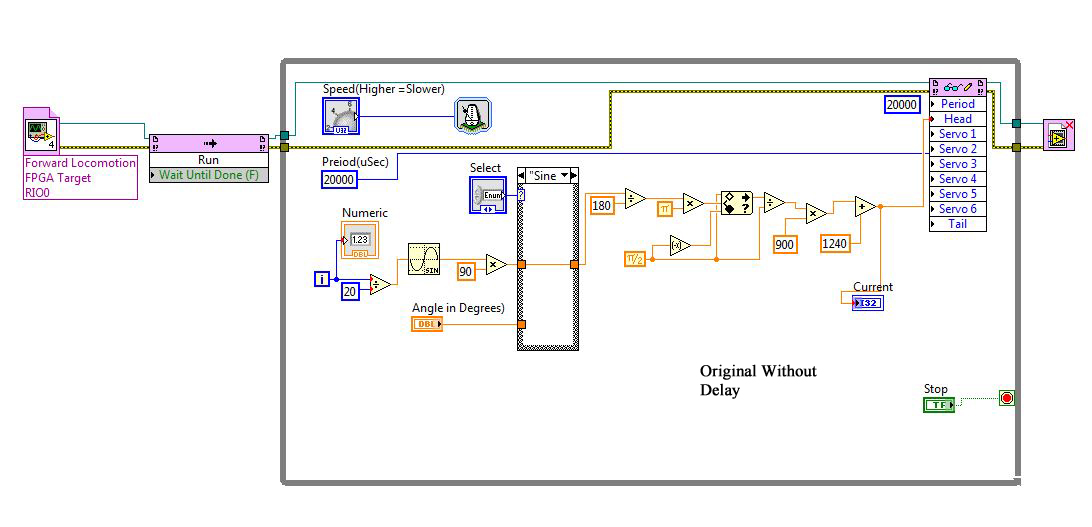

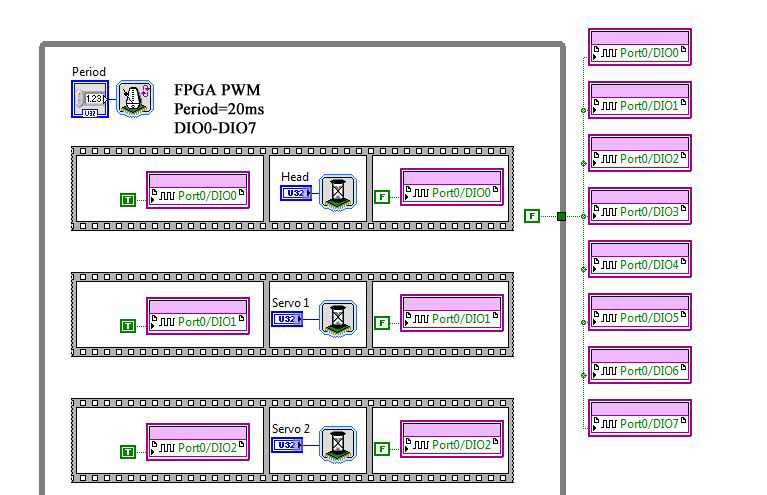

First and second picture shows the FPGA linked to an RT. Im trying to introduce a certain delay after "Head" is executed before Servo 1 is started. And delay again before Servo 2 started and continues to Servo 3,4,5,6, and Tail. It is a while loop until a control stop is pressed.

Question is, should the delay be put inside the FPGA or RT host?

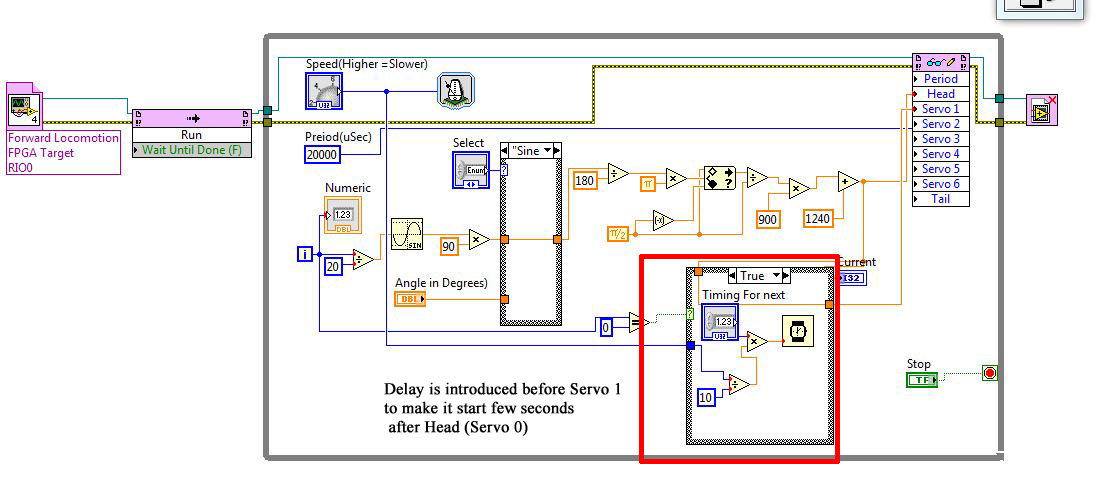

I tried this in the picture below but failed

I need some idea on how to do it. Totally stuck right now...Thanks in advanced

05-03-2013 07:00 AM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

How much of a delay do you want? It seems like what you really want to do is make your FPGA code more linear, not parallel.

There are only two ways to tell somebody thanks: Kudos and Marked Solutions

Unofficial Forum Rules and Guidelines

"Not that we are sufficient in ourselves to claim anything as coming from us, but our sufficiency is from God" - 2 Corinthians 3:5

05-03-2013 08:03 AM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

it's best if the delay is connected to a control. The delay I wanted is 1ms.

its put that way because i need to control each individual servos

05-07-2013 02:49 AM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

anyone got any ideas?

05-07-2013 03:20 AM - edited 05-07-2013 03:21 AM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

Hi august,

your delay is located before the FPGA property node. The node will be executed after your delay: DATAFLOW RULES!

You should have one FPGA write node to set a new "head" value, then wait, then set the "servo" values...

05-07-2013 03:32 AM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

05-07-2013 03:34 AM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

05-07-2013 03:48 AM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

so you're saying i should create another while loop with delay for controlling servo 1 parallel to the one controlling the head?

i prefer not to disturb the codes in fpga if possible

05-07-2013 03:51 AM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

05-07-2013 07:30 AM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

@augustg wrote:

so a total of 8 different fpga's?

No. 8 different FPGA Property nodes. You can then put in a Wait before each one to create the delay you want.

Or, as I was saying before, create a sequence in your FPGA with the delays you want before each write to an output.

There are only two ways to tell somebody thanks: Kudos and Marked Solutions

Unofficial Forum Rules and Guidelines

"Not that we are sufficient in ourselves to claim anything as coming from us, but our sufficiency is from God" - 2 Corinthians 3:5