- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

Hilbert transform (90 degree phase shift) on FPGA-using FIR filter

Solved!09-25-2017 11:15 PM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

Hi,

I want to shift 90deg-phase of the input signal on FPGA. I am utilizing a NI-PXIe 7279R module with a NI-PXIe 5733 ADC converter on FPGA unit.

At first, I want to record a sinusoidal signal with a frequency of 2.7 MHz from my system. Then I want to shift to 90deg to extract both I and Q signals. So I am intending to use FIR filter for generating HILBERT transformer.

Now I am following the "Polyphase Interpolation FIR Filter on FPGA with DFD and Coregen". They showed at the link https://forums.ni.com/t5/Example-Program-Drafts/Polyphase-Interpolation-FIR-Filter-on-FPGA-with-DFD-...

I used an example: FFT project with FPGA Target (RIO, cRIO-9075, simulation) in the "Find Examples" of LABVIEW help for SIMULATION (2.HlBERT-FPGA.zip).

However, I can not know how to transfer the output of Hilbert transform (the 90deg-phase shifted signal) to HOST. So I can not compare the phase between Quadrature signal and Original signal. Even I also do not know that the Hilbert transform using the FIR filter is true or not.

Please help me to correct this program and give me some advice.

Thank so much.

Dong

Solved! Go to Solution.

09-26-2017 03:20 AM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

09-27-2017 11:33 AM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

Hi Dong,

There are a few methods that you can use to transfer data to your host for further processing. How is your data represented on your target and how much data do you need to stream back to the host? What have you tried thus far and what issues have you run into?

10-01-2017 09:19 PM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

Hi crdub09, wiebe@CARYA, James_McN,

I am following a Hilbert algorithm that shown in an attached Algorithm file.

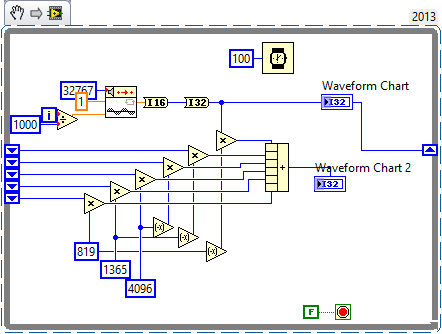

I generated a LABVIEW program that is based on the structure algorithm above; however, it seems to be wrong. Please help me.

Thanks

Dong

10-02-2017 02:14 AM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

I'd think there might be (at least) some saturation issues. The values from input are I16's. But if you multiply them with another I16, they need a I32 to fit. After adding the 6 I32, they might fit in an I16.

You can use doubles on FPGA (I'd expect large compile times and need for resources), maybe just to get things working? Did you get this working on the host? If you replace the Z-1 nodes (delays?) with feedback nodes, it should work on a host. This would save you a lot of compile time to get it working. Once it works, put it on the FPGA.

10-02-2017 02:42 AM - edited 10-02-2017 02:43 AM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

And also you need to be more accurate.

Between a4 and a5 is only one delay, as there is between a5 and a6. In your code there are always 2 delays.

Never mind.

10-02-2017 02:48 AM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

10-02-2017 03:03 AM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

@ThanhDong wrote:

Thanks wiebe@CARYA ,

From my program, you mean the output is I16?

After the fixed point multiplication, don't convert to I16. A (max) I16XI16 won't fit an I16.

Not sure why you need fixed points anyway. If the Z-1's are polymorphic, convert the input to I32, and delay the I32. A feedback node or shift registers should work too. Then multiply the I32 with I32 constants. This will work, because you know the I32 never have values >2^15 (I16). The fixed point math just complicates the code.

10-17-2017 07:41 AM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

Dear wiebe@CARYA ,

Thank so much for your helping.

I try to make a design using Z-1 elements, and it seems to effectively operate.

Thank you.

Dong