View Ideas...

Active

Inactive

Inactive

Turn on suggestions

Auto-suggest helps you quickly narrow down your search results by suggesting possible matches as you type.

Showing results for

Options

- Subscribe to RSS Feed

- Mark as New

- Mark as Read

- Bookmark

- Subscribe

- Printer Friendly Page

- Report to a Moderator

Simplify the display of Single Cycle Timed Loops in LV FPGA

Submitted by

gsussman

on

10-16-2009

10:39 AM

9 Comments (9 New)

gsussman

on

10-16-2009

10:39 AM

9 Comments (9 New)

Status:

New

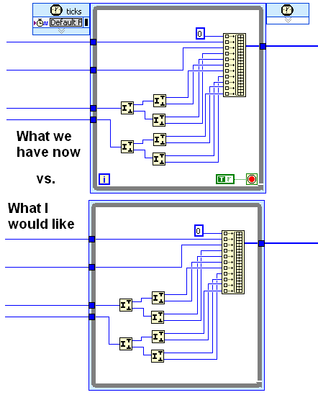

Single cycle timed loops are a huge performance enhancer in LV FPGA. We learn to use these very prolifically in and around our code to save precious FPGA space, yet the BD representation of the SCTL is the standard Timed Loop structure, with both the Left and Right "ears" visible as well as the conditional terminal.

I propose that the SCTL be given it's own representation on the block diagram, one without the "ears" and without the conditional terminal (by definition it only runs once). This will promote much cleaner looking FPGA code and more readable diagrams.

Greg Sussman

Sr Business Manager A/D/G BU

Sr Business Manager A/D/G BU

Labels:

9 Comments

You must be a registered user to add a comment. If you've already registered, sign in. Otherwise, register and sign in.