- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

URSP 2953 synchronous TX-RX

04-07-2017 05:14 PM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

Hello everyone,

As a begginer in Labview programming, I intend on designing a pulse radar platform. I know this issue has been addresed in a few topics so far; I have read most of them.

Briefly, I want to transmit a chirp signal and receive the delayed signal. For my purpose, it is critical that the TX and RX must start at the same time instance, or at a constant time delay.

I have started with the Labview FPGA example "Tx and Rx streaming (Host).vi" and modified it to fit my purpose.

The problem I am having now is the triggering section. I have tried to use the advice in post nr. 9 in topic https://forums.ni.com/t5/forums/v3_1/forumtopicpage/board-id/500/thread-id/2082/page/1

by setting the TX trigger as: "Rx start trigger" and the Rx start trigger as "Immediate".

If I run the vi continously, some RX pulses are missed at all, while some suffer from a random delay.

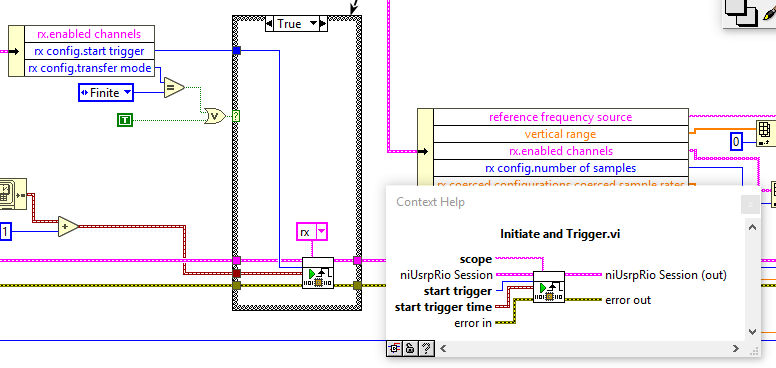

On the first hand, I do not understand the role of the timestamp for the "Initiate and Trigger.vi" from the snapshot.

Can a FPGA implemented trigger solve my issue? Is it more precise than the one implemented in the example?

Thanks for your help,

Mihai

04-08-2017 07:01 PM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

I have understood that the "Initiate and trigger.vi" uses the input timestamp only in the case of "Future time event" trigger selection.

Still, a lot of questions remain.

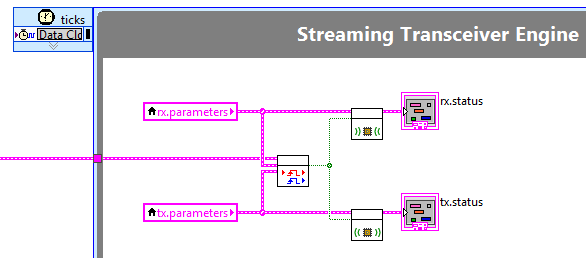

1) I have tried to use a single trigger for both the tx and rx side, in the FPGA vi (see the picture). I still do not get better results.

2) Is there a way to test the obtained trigger signals on the FPGA using the available USRP GPIO's or LED? How can I be sure that the TX and RX start at the same time?

Thank you!

04-10-2017 06:16 PM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

Hello Minhai!

I wanted to take a step back and understand your application. you mentioned that you are trying to implement a pulse radar platform. Could you elaborate what you mean by this? Additionally, what is connected to the front terminals of the USRP 2953?

Also, you mentioned that you need the Tx and Rx need to be synchronized and start on the same time instance. To clarify, you want the Tx and Rx to start on the same sample clock pulse, correct?

In response to your original questions, in the screenshot of code you attached, there is a blue constant that says "Finite" on the far left. As you mentioned that you are running this continuously, you may want to change that to say "Continuous". This should help mitigate some of what you are seeing. The same will go for the Tx Streaming (Host).vi in the project.

I hope this helps!

Best,

Casey L.

Applications Engineer

04-11-2017 02:29 PM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

Hello Casey,

By pulse radar I meant a radar that transmits a finite duration impulse of RF energy. The impulse has linear frequency modulation (chirp). The chirp is generated in the baseband and then upconverted on the carrier. The received impulse comes with a delay proportional to the radar-target distance. The cross correlation between the TX chirp and the RX (delayed) chirp yields the range profile.

The front terminals of the USRP connect a long coaxial cable loopback. The tx port for RF0 is tied to the rx port of RF1 channel.

Issue 1: I do need too make sure that the TX and RX start at the same sample clock pulse.

Issue 2: For now, I am able to run the vi several times, but sometimes I receive an error which states: Error in Invoke method: FIFO.Read in Fetch Rx Data (U32).vi. This error comes irregularly and does not happen on every run.

Thanks for your answers,

Mihai

04-12-2017 09:20 PM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

Hey Mihai!

Thank you for clarifying your application and set-up!

From my research, the example in this forum post may be more beneficial for achieving synchronization with Rx and Tx.

Additionally, the reason why you are seeing the error occasionally is likely due to stopping the Tx VI before the Rx VI.

I hope this helps!

Best,

Casey L.

Applications Engineer

04-13-2017 05:02 PM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

Dear Casey,

The example in the post shows exactly why synchronization is not achieved. If you run the vi several times, you can see the phase of the received signal changing in the "Receive I/Q plot" from one run to another. This shows that there is a processing part which does not have a fixed duration, somewhere on the TX or RX chain.

The example also uses the vi-s from the NI-USRP section. I am now using the drivers in USRP RIO section, since I have noticed them to be suitable for host-FPGA interaction.

In my project, am using the same vi for both TX and RX.

Best regards,

Mihai

05-15-2017 10:38 AM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

I have continued my project and migrated it to the FPGA as much as possible. So far, I am using a preinitialized memory for the TX data and an empty memory for RX data. Now, the host's only purposes are sending the trigger for the start of TX data and the trigger for reading the RX memory, which comes significantly later. The RX memory is read using a FIFO.

Even if this implementation is considerably more compicated than the host only version, it does not seem to improve performance over it. I still have the same phase drift as the one recorded in the host version. This may be the capabilites of the USRP hardware. I will investigate further.

02-25-2019 06:59 AM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

Hi Mihai,

I know this is a bit of an old post, but I was wondering if you've made any headway on this.

I am struggling with the same issue and it would be great if you could share your solution/findings.

Warmest Regards,

HoSsEiN

02-26-2019 04:27 AM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

Hi Hossein,

I have accepted the phase synchronization error as is. It think it is related to hardware and cannot be overcome.

02-27-2019 12:20 AM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

Hi Mihai,

Thanks for getting back to on this, it's sad to hear this!