- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

sbRIO-9632 Non path timing violation

01-16-2019 01:02 PM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

Hi.

I am currently working on my diploma thesis which main topic is to build functional HIL test stand.

Recently I am starting to occur error which I cannot get rid off and it makes me crazy.

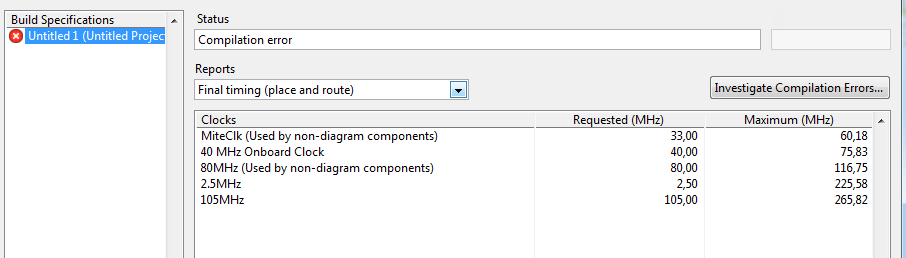

The main problem is with compiling program. It seems that all requirements are completed successfully, but in the end i got non path timing violation.

Main idea is to have program, where are three separated loops. One SCTL for PWM generation on high frequency (110 MHz), second one SCTL for real time model computation (like 2.5 MHz) and third one basic while loop for ADC converters. Everthing works fine until i added ADC to the loop. Than it starts producing this report. Does anybody know where could be the problem ? I was even trying to compiled basic program where was just two ADC and SCTLs contains just simple increment and it still result in fail.

I have tried also to run same program at cRIO 9073 and it result in same fail. What seems interesting for me that its run OK on myRIO 1900.

What is also interesting, each xilinxlog ends with "Process "generate programming file" completed successfully".

I am using

Target Class: sbRIO-9632

FPGA Device Information:

Family: Spartan-3

Type: xc3s2000

Speed Grade: -4

Package: fg456

Compiler Information:

Version: Xilinx 14.7

Xilinx Options in Build Specifications: Supported

Thanks for any help.