- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

High speed data logging CRIO 9035

09-27-2017 04:03 AM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

Hello guys,

I am looking for a high speed data logging application using CRIO 9035. I am using the FPGA VI to draw samples out of the analog input(AI0 in NI 9220) and store in a FIFO. Then, I use the Real time VI to invoke FPGA and create a tdms file. I have compiled the fpga vi using cloud servers. When I run the RT VI, I either get all the values to be zero or an error out saying error code -61003. When I run the FPGA vi in simulated input output mode, I see that the VI works and I can see through the probe that the analog input is being read. But, when I use RT VI, the FPGA code does not work or gives wrong answer. I am attaching the image files of the two VIs. I would be really grateful for some help.

09-27-2017 04:17 AM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

For issues like this, it is helpful for us if you attach the actual code, including the project file. There are just too many factors hidden from the images.

But my shot in the dark says you have an issue with the Load FPGA.

There are only two ways to tell somebody thanks: Kudos and Marked Solutions

Unofficial Forum Rules and Guidelines

"Not that we are sufficient in ourselves to claim anything as coming from us, but our sufficiency is from God" - 2 Corinthians 3:5

09-29-2017 01:55 AM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

Thanks for the reply, I am attaching the codes in this post. Even I felt the problem is with the load FPGA. In case, there are any files missing, just let me know. I would be really grateful for some help as it is bogging me down for some time.

09-29-2017 02:05 AM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

Just to be on the safe side, I have attached the entire project folder as a zip file in this post.

Thanks in advance

09-29-2017 06:15 PM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

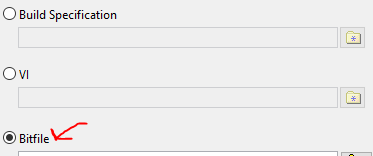

Just looking at the Open FPGA Reference, a couple of things to try:

1. Turn OFF the "Dynamic mode". You are not doing anything making that necessary.

2. Open the bitfile. That will make sure you have the latest compiled version.

There are only two ways to tell somebody thanks: Kudos and Marked Solutions

Unofficial Forum Rules and Guidelines

"Not that we are sufficient in ourselves to claim anything as coming from us, but our sufficiency is from God" - 2 Corinthians 3:5

10-01-2017 05:08 AM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

Tried these steps but it does not work. Can you guide me how to run both fpga vi and RT vi step by step. As I am new to labview, I could have missed something obvious! By the way, thanks for help in advance.

10-11-2017 02:33 AM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

Hi shantanu1088, I just noticed a mistake in your code. In the filepath you have forward slashes / but what you actually want is backward slashes like this \.

So you path should read c\whateverfolder\logdata.tdms

10-12-2017 12:52 PM - edited 10-12-2017 01:01 PM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

I tried running your code and it basically worked fine for me. I was able to make a TDMS file and transfer it using FTP

The most straightforward way to access the FPGA IO is to use the bitfile in the Configure Open FPGA VI dialog.

In your FPGA, if you set the loop timer to 1 us, the loop timer will do a 0us wait because your analog input takes longer than 1 us to acquire. You could remove the loop timer.

Your FIFO read architecture requires high CPU use. This article explains why.

Maybe add an indicator to the analog input and error terminal on the FPGA so you can see if that's all OK. It could just be a hardware error.