- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

1422 documentation

06-25-2019 03:08 PM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

Hi I am trying to resurrect a custom single x-ray photon counting camera system that has a 1422 frame grabber...

Yes I know it is no longer the state-of-the-art. I cannot upgrade as there is no funding to buy new hardware.

I cannot find documentation---many of the links that reference it are "dead" eg in this thread:

I remember there were peculiarities in the device needing continuous pixel clocking even when line synch/enable

was inactive and that line synch had to be unselected for three pixel clocks. This information is not present on the users manual.

Help!!!

Thanks

06-26-2019

12:42 PM

- last edited on

11-18-2024

08:49 PM

by

![]() Content Cleaner

Content Cleaner

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

Hi Caribou,

Thanks for reaching out. It's a cool application you have. I'm not sure how helpful we can be with some of the older cards since a lot of the knowledge has moved on, but maybe we can be of help.

Here are some of the links I found:

What are the Timing Requirement of a the 1424 and 1422?

Hopefully this helps! Goodluck!

06-26-2019 12:53 PM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

Hi.

Thanks for the response

My issue is that the critical links (like the second one in your list)

are *dead* --- that is they bring me to an inactive page.

How can I find that info??

We need to go back and demonstrate performance of sensor before we have a chance for more

$$---- then we can upgrade to cameralink

06-27-2019 12:35 PM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

Hi caribou,

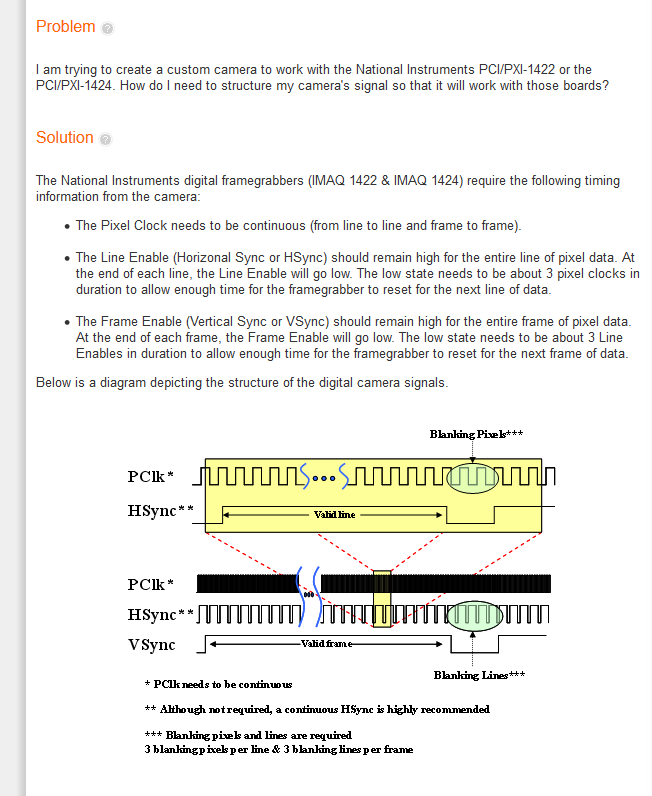

I apologize, the ones in the original post are all broken for me, but the ones I posted, all work on my network and browser. Let me know what one's don't work for you. I uploaded an image of the content of the second link. Hopefully it helps.

Staff Software Engineer

National Instruments

06-27-2019 03:10 PM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

Thanks!!

That was the diagram that I remember.

So pixel clock has to be continuous.... but the frame synch only has to go low for approximately

a **time period** equivalent of three lines--even though a continuous hsync is recommended.

I have the system running but it is un reliable and inconsistent---it runs for a while but then loses synch and

gives me a time out error.

-

06-28-2019 11:11 AM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

Caribou,

So pixel clock has to be continuous.... but the frame synch only has to go low for approximately

a **time period** equivalent of three lines--even though a continuous hsync is recommended.

This is correct.

I have the system running but it is un reliable and inconsistent---it runs for a while but then loses synch and

gives me a time out error.

If you post your code, maybe we can see if it's a software issue. Otherwise make sure all of your cabling is functional.

Staff Software Engineer

National Instruments

06-28-2019 04:34 PM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

Well it is not code in so much as it is firmware. I hope you can understand the following description.

Camera is FPGA based with a 16bit adc. It operates in vacuum chamber. ---Since LVDS output eats up

pins on our vacuum feed-thru, we are sending the pixel data to frame grabber as pairs of double bytes.

The pixel clock is being double tapped so for two pixels it looks like: ____--__--___________--__--____

one pixel's byte1 and byte2 in rapid succession then the next pixel's two bytes etc etc.

--this is all happening when line sync is asserted. We operate frame grabber as if we had a byte camera, and then

recombine bytes into a words offline.

During the time period that the line sync is not asserted, we send a bunch of regularly spaced pixel clocks.

My gut feeling is that the frame grabber does not like the double taps and would prefer to have everything

more regular.

Let me know what you think

Thanks again for the comments

07-01-2019 10:57 AM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

It should be able to accept Double Tapped 16 Bit signals. I don't know if I can comment if the the 1422 prefers just a standard high/low pixel clock, but I'd just recommend that you double check you are operating everything within spec.

Staff Software Engineer

National Instruments