- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

cRIO Consumer Producer FPGA RT 100 kHz

01-18-2010 11:05 AM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

01-18-2010 11:57 AM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

Hello,

Thank you for the responses. So, I should keep using the flush queue command, go through the 1-D array of clusters, and concatenate the arrays from the clusters together? That sounds awfully complicated, but I can try to figure out how to do that if necessary. It seems like there should be a better way.

If I simply wire the prepend array or string size to false, will that take care of some of my problems?

Also, I am not sold on fixed point, but the data from the analog input NI 9215 module comes out as fixed point <+/-, 20, 5>. That said, now I am confused, why it would come out as 20 bit information, when the module is 16 bit. With respect to writing to a file in fixed point format, I didn't want to perform an unnecessary conversion, which might slow things down. If writing to a file will be easier in some other format, please let me know. I understand that I could also reduce the number of bits of fixed point as well.

As for a waveform chart, the prior versions I showed included the waveform chart, but I took out the waveform chart when I couldn't get the flush dequeue to interface easily with it. This system is going to be used for experiments, in which it would be useful to see waveforms (possibly without all the data) to know things are functioning properly. Okay, thank you again for your help.

Aaron

01-18-2010 12:05 PM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

Hello,

Thank you for the link. I had downloaded this before, but I didn't find it helpful.

1. Certain modules seem to be missing when I try to load it in my current version of LabView (2009).

2. I would prefer to save the data directly to the cRIO and then FTP the logged files to my laptop. Having talked to NI support, it seems like this will be safer in terms of getting all the data at the bandwidths I desire. I am also planning to get a NI 9802 for our lab, if I can get things to work. Is this a more expensive solution? Probably. More reliable? Hopefully.

Please correct me if I am wrong in my observations. I appreciate the help.

Aaron

01-18-2010 03:36 PM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

Hello,

So, I tried the simple test of just wiring a false to the prepend array or string size? input on the write to binary file using dequeue to see if that would help things any in terms of the "jumping" I see in my file output. Unfortunately, I do not see any improvement. I have attached the processed text file and an image of the implementation (hostread13vi.jpg).

Also, any insights on how to adequately process data coming from a dequeue or flush queue would be appreciated. For the flush queue, I looked at trying to use the array to cluster and cluster to array, but I didn't make much progress. I am also not quite sure how to unbundle the cluster coming from the flush queue. I have attached an image (hostread12withcontexthelp.jpg) with the context help describing the remaining elements coming from flush queue. Thank you everyone for your help, and I await further insights.

Aaron

01-19-2010 11:20 AM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

Hello,

I am able to save 5 16-bit (integer) channels to a binary file at 100 kHz and then recover the data (see attached images). I did this by converting the fixed point <+/-,20,5> stream to I16. However, I am only using a very small portion of the range that the 16-bit integer offers. How can I efficiently convert the fixed point <+/-,20,5> to a 16-bit integer or other type, which I can then write to a binary file? Should this be done at the FPGA level or in real-time?

The pdf file shows five channels, which have been extracted from the written binary file. The top channel shows a 10 Hz sine wave from a signal generator. The sine wave goes from -5 to +5 (half the total range from -10 to +10 V of the NI 9215) and you can see the quantization. With a 16-bit integer (-32768 to 32767), it would be better to have the sine wave going from-16384 to 16383 or something like that.

Getting closer. Thanks.

Aaron

01-19-2010 03:17 PM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

Hello again,

I have tried the following implementation at the FPGA level, which works more or less. Is there a better way to convert from the fixed point <+/-,20,5> to 16 bit? The attached graphs were sampled at 50 kHz, and you can see some jumping. At 100 kHz, there is a simpler jumping. Channel 1 should show a 10 Hz sine wave. Thanks.

Aaron

01-20-2010 05:07 PM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

01-21-2010 11:33 AM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

Hello,

Thank you for the response. To your point about converting from one representation to another. I am a little bit confused about the NI 8215, which I think is a 16-bit device. The board seems to be delivering FXP <+/-, 20, 5>, which are 20-bit numbers, right? If I want the bitwise equivalent as discussed in this article (http://zone.ni.com/devzone/cda/pub/p/id/363), how do I go about doing that? Yes, I would like to convert, but I'm not quite sure how. Thanks again.

Aaron

01-21-2010 11:51 AM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

Hello,

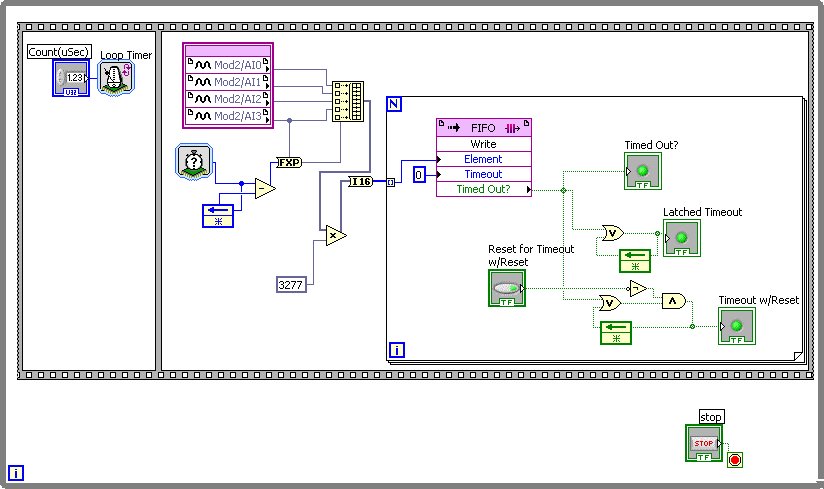

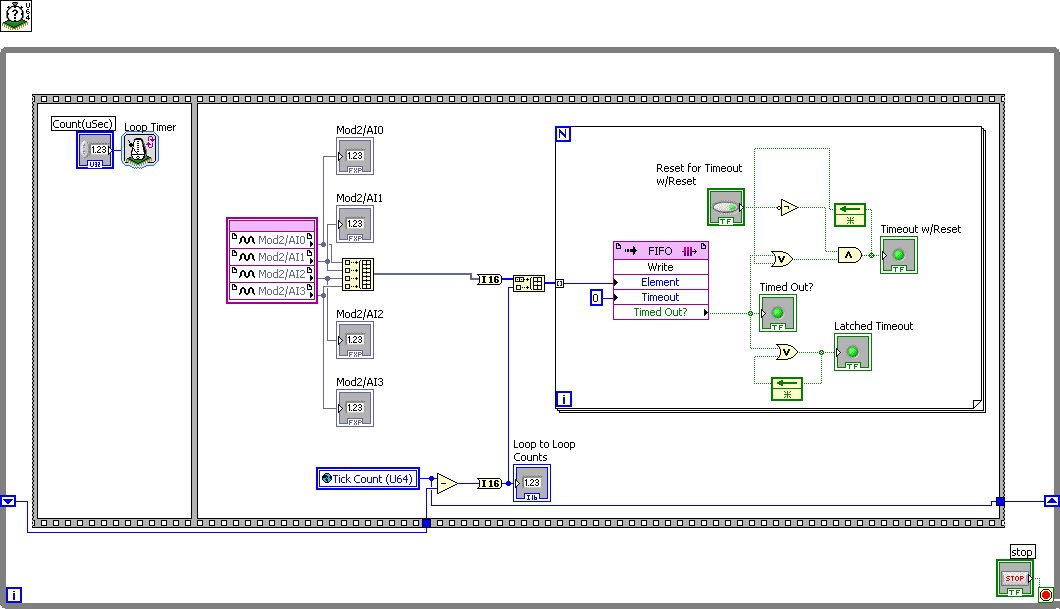

I have another issue, which may or may not be related. When I implement this VI (image below) on the FPGA without any host vi running (DMA FIFO is full), I get the following results for Count (usec) and Loop to Loop Counts.

Count (usec) Loop to Loop Counts

10 440

11 440

12 480

20 800

40 1600

80 3200

100 4000

The analog inputs are from an NI 8215, which should run at 100 kHz. I would like to be able to get 400 ticks for 10 usec with the 40 MHz clock. Should I just be content with 440 tickes with the 40 MHz clock, which comes out to a sampling rate of 90.9 kHz? Thanks.

Aaron

01-22-2010 12:20 PM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

FIrst of all I'm assuming that you are referring to the NI 9215 16 Bit analog input module becasue there is no NI 8215 C series module. Second to get the 16 bit data you need to change the properties of the module. In your project, right click the module and select properties. Then change the Calibration Mode from Calibrated to Raw. You will now get the raw data output directly from the ADC (I16 value).

For your second question, the rest of your code inside the second sequence structure is probably taking longer than 11 uSec to complete. If you want a faster rate, try removing some of the extra code, otherwise you'll probably have to be content with 90.9 kHz.