- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

Xilinx Block Ram with VHDL

11-21-2014 12:51 PM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

I am currently trying to interact with the Block RAM in Xilinx Spartan 6 FPGA. In the IP Integration Node, I have a large chunk of VHDL codes that need to access to the Block RAM. I understand there is a Xilinx Core Generator so I can create a BRAM in Block Digram; However, I would like to access to the BRAM in the VHDL code. Have anyone tried to access to Xilinx BRAM with VHDL before?

11-21-2014 01:13 PM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

Are you wanting to access the Block RAM from both the G diagram and within the VHDL? It would be helpful to have a high-level picture of what needs to communicate with the RAM.

11-21-2014 01:16 PM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

Thank you for yoru reply.

Not Both. I just want to access within the VHDL code. So currently, I have a large chunk of VHDL code which the BRAM acess is not programmed. I would like to finish the VHDL code so that the VHDL code is fully programmed with access to BRAM, and I can call this VHDL code with IP node in LabVIEW.

11-21-2014 02:14 PM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

In that case using the Block Memory Generator is fine. When you import the VHDL into an IPIN node in LabVIEW FPGA make sure to include those generated files in the IPIN configuration.

As far as using the block memory in VHDL, the Block Memory Generator will generate a template I believe which shows how to hook it up. If not there are numerous resources online with how to instantiate VHDL entities and call them.

11-21-2014 07:22 PM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

Ya I have tried these generated files but it didnt work. Do you have any resources that I can refer to?

11-24-2014 11:21 AM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

Anyone has experiences with this?

11-24-2014 11:42 AM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

Well, I don't have experience with this specifically, but I do have a recomendation:

Get your VHDL working in ISE/whatever IDE you use, build it into an NGC, and call that via the IPIN/CLIP Node. I've found this generally easier than trying to reference a bunch of support files in the nodes. If you're using CLIP, I believe you'll have to create a VHDL wrapper that calls into the NGC, and include the NGC as a support file.

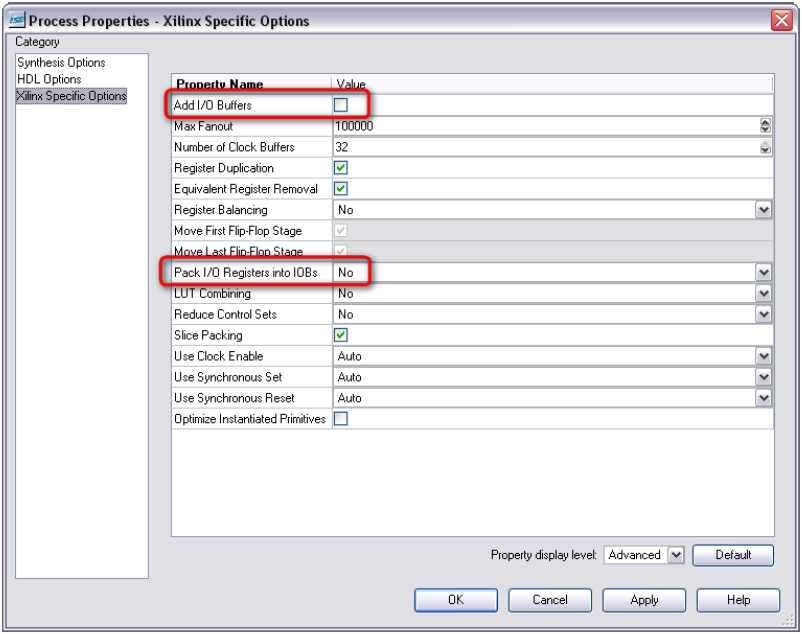

Also, in your build settings in ISE, you'll need to uncheck "Add IO Buffers" and set "Pack IO registers into IOBs" to no.

Hopefully that lets you work around any file dependency issues.

TJ G

11-25-2014

01:02 PM

- last edited on

04-11-2025

06:20 PM

by

![]() Content Cleaner

Content Cleaner

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

You might also try the built in Xilinx blocks that are configurable from within LabVIEW FPGA. There is a palette specifically dedicated to Xilinx core generator blocks. https://www.ni.com/docs/en-US/bundle/lvfpga-api-ref/page/menus/fpgacategories/programming/xilinx-ip-...