- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

Terminal type of source is "long", sink is "void"

Solved!06-28-2013 09:55 AM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

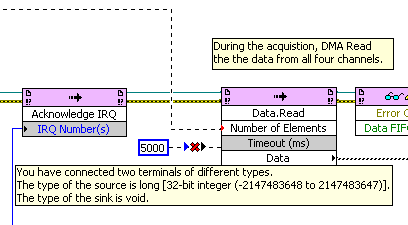

Hi, I have wire to an "Invoke Method" block, but I'm getting the following error shown in the picture.

I was wondering how I can solve it.

Solved! Go to Solution.

06-28-2013 10:45 AM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

Data probably isn't a valid DMA FIFO. It needs to be a Target to Host DMA FIFO.

Can you zip up your project and post it? That would be easier to debug.

There are only two ways to tell somebody thanks: Kudos and Marked Solutions

Unofficial Forum Rules and Guidelines

"Not that we are sufficient in ourselves to claim anything as coming from us, but our sufficiency is from God" - 2 Corinthians 3:5

06-28-2013 12:31 PM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

Sure, please find attached my project files.

Sorry, I couldn't make a ziped file as I got a corrupted file massage!

06-28-2013 01:08 PM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

Yep, you don't have a DMA FIFO in your FPGA target. So trying to read a FIFO called Data that doesn't exist will cuase this problem.

There are only two ways to tell somebody thanks: Kudos and Marked Solutions

Unofficial Forum Rules and Guidelines

"Not that we are sufficient in ourselves to claim anything as coming from us, but our sufficiency is from God" - 2 Corinthians 3:5

06-28-2013 06:52 PM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

Nice help. I'll try to solve the problem. I'll ask if I run into a problem in defining the DMA FIFO.

07-01-2013 09:54 AM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

Hi, the following picture shows a block in the FPGA target code.

The documentation of that block says "6. Write the measured data to the DMA FIFO."

I was wondering why this DMA FIFO is not working and how I can define the appropriate DMA FIFO in the FPGA target.

07-01-2013 10:23 AM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

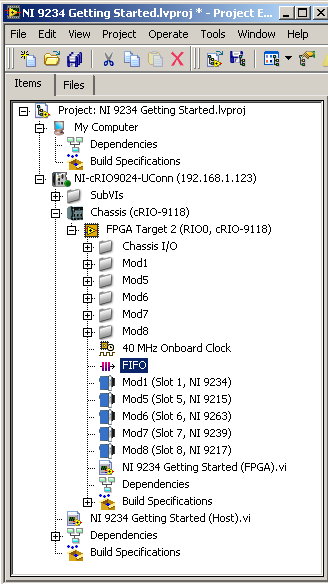

I created a DMA FIFO in the project as shown in the following figure.

Now I'm going to check if it solves the problem.

07-01-2013 10:30 AM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

If you haven't created a FIFO yet, right-click on your FPGA target and select New->FIFO. If you have the FIFO created, you can double-click it in the project window to open the properties dialog.

There are only two ways to tell somebody thanks: Kudos and Marked Solutions

Unofficial Forum Rules and Guidelines

"Not that we are sufficient in ourselves to claim anything as coming from us, but our sufficiency is from God" - 2 Corinthians 3:5

07-01-2013 10:33 AM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

After creating a DMA FIFO in the project explorer, now the problem is solved and the wires are not broken as shown in the following window.