- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

Need help with problem using PID in FPGA

04-20-2016 11:10 AM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

Hi,

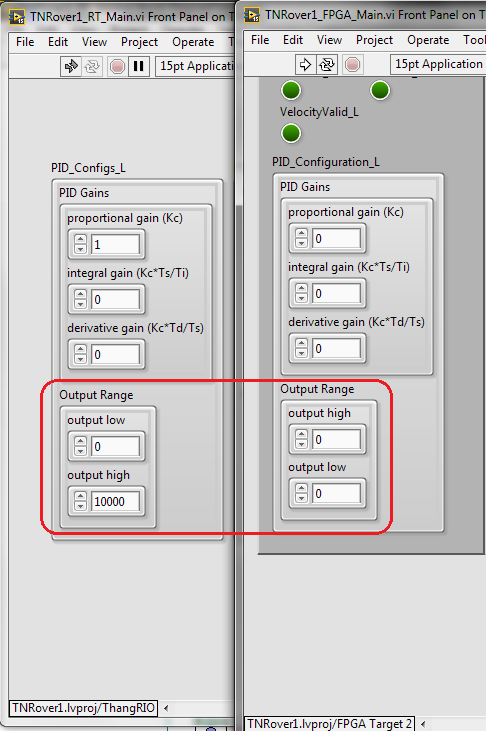

I use FPGA to generate PWM signal to drive a DC motor. The PWM will be generate based on High_Cycle_Count = Pulse_Offset(tick count) + Delta_Pulse_Width(tick count). My PID control output is the Delta_Pulse_Width. The input is Velocity (tick count/interval). I don't understand why when it start both the set velocity and the current velocity is 0 but the output of the PID is the High Limit Value of the PID setting.

I attached the screenshot of the PID portion.

Thank you for your time reading and answering my question.

04-20-2016 11:54 AM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

Could you upload your actual VI? I don't see an obvious problem but perhaps there's something in the configuration of your PID, or in the values you've chosen.

04-20-2016 12:04 PM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

Please find in attachment is the zip file of my project. The configuration is sent from TNRover1_RT_Main.vi. I just set Kc to 1 and other to 0. Low limit is 0 and high limit is 10000.

04-20-2016 12:40 PM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

I opened your project, right-clicked on the myRIO target to set the execution mode to simulation (since I don't have a myRIO), entered the values you mentioned on the front panel (see screenshot) and ran the VI. I don't see the behavior you describe. Can you check that when you run the FPGA VI alone (in simulation, and on the myRIO) that this doesn't happen? I suspect the issue is somewhere in your RT code, and has nothing to do with the FPGA PID.

04-20-2016 01:18 PM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

Nathand: I will do some debug tonight and I will update you. Thank you very much for helping me.

04-23-2016 12:52 AM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

Nathan:

I still cannot find out the bug yet. When I run my RT VI, both motors run immediately at very high velocity even the set velocity is 0. The delta returns 10000 which is highest value. I then set to a small value then both motor stop.

When I ran in simulation mode, delta just 0.

04-25-2016 12:47 PM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

It appears that your problem is that your Output Range cluster on the RT side doesn't match the Output Range configuration on the FPGA. The ordering of the "output low" and "output high" are swapped. LabVIEW doesn't flag an error because the cluster datatypes match - both Output Ranges are clusters of two numbers - but the values themselves are backwards. You need to re-order the cluster in one of the Type Definitions so they both match. Open the type definition, right-click the border of the Output Range cluster, Reorder Controls in Cluster.

04-25-2016 05:52 PM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

I should clarify. Make sure you change the one that doesn't match the PID input, so that it does match after your edits! If you make the two clusters match each other, but don't make them match the expected input to the PID function, then you'll still have the same problem.

04-27-2016 01:38 AM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

Nathan,

Thank you very much. I made the PID configureation a typedef now so I don't have problem with not match control anymore. Actually I made 2 different typedefs accidently so they didn't match.

The PID start response now. I am working on tuning the PID. But while working on tuning I have an issue which made me really confuse. If I just run the Real Time VI only the system does not work, I have to run the FPGA VI to have it work. Does it mean there is something wrong with the way I load my bitfile?

Regards,

04-27-2016 12:13 PM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

Have you checked all the error wires out of the FPGA Open, FPGA Run, etc? That would be the first place to look to see if there's a problem with the way you're running the FPGA. You can also run the FPGA in interactive mode while you're running the RT code - start the RT application, then once it's running click the Run arrow on your FPGA VI (this works with some RIO targets, I do not know if it works for all of them). Then you can watch whether changes you make on the RT front panel are updating the FPGA.