- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

NI GPS 9467 timestamping

01-21-2016 07:19 AM - edited 01-21-2016 07:19 AM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

Hi all,

I am trying to use the NI 9467 GPS card for my crio system (NI 9066) to timestamp waveform measurements using NI 9239. Is there some example on how to intergrate the GPS time into the waveform using the timekeeper vi's? I saw the timekeeper examples but it is not clear.

Thankl you,

01-22-2016 12:29 PM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

Hi TinoMK,

Were you referring to this FPGA Timekeeper example linked from the related KnowledgeBase article about using the FPGA Timekeeper to Synchronize Data with the NI 9467? What do you find unclear about the example?

There's also another Community Example that takes sample timing from the GPS synchronized with Timekeeper that may help if you have not seen it yet.

Lauren

Applications Engineer

National Instruments

01-25-2016 03:21 AM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

HI Lauren,

Thank you very much for your help. I will try the example and let you know how it works.

I saw the examples for the Timekeeper but it was not clear how to integrate that into my existing code and have timestamping from the NI 9467 GPS card. Mainly I use the Delta Sigma Continous acquistion (pipelined) example as the basis for my application.

Thanks again,

01-26-2016 11:09 AM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

Hi TinoMK,

I believe you could integrate the Timekeeper VIs in with the code under the FGPA target. After glancing through the Syncrhonize to GPS example, it looks like you could add a sequence structure after the synchronization for data acquisition. You could format the data acquisition similar to the way data is acquired through the FIFO in the NI 9234 Cont Acq (FPGA).vi in the Delta Sigma Continuous Acquisition (pipelined) shipping example project. You would also need to place the FPGA Timekeeper VI in the top level outside of all structures.

Lauren

Applications Engineer

National Instruments

01-26-2016 11:20 AM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

I have already tried the integration and would appreciate your comments to the pictures of the code that I will post tommorow.

I made changes at the FPGA part and also on the RT part of my application( actual timestamping of the data). I will have a chance to try the code in 2-3 weeks when I go the field so would like to be as much as I can sure of the changes I did.

Thanks again and will post tommorow.

Regards,

01-27-2016 06:18 AM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

Hi Lauren,

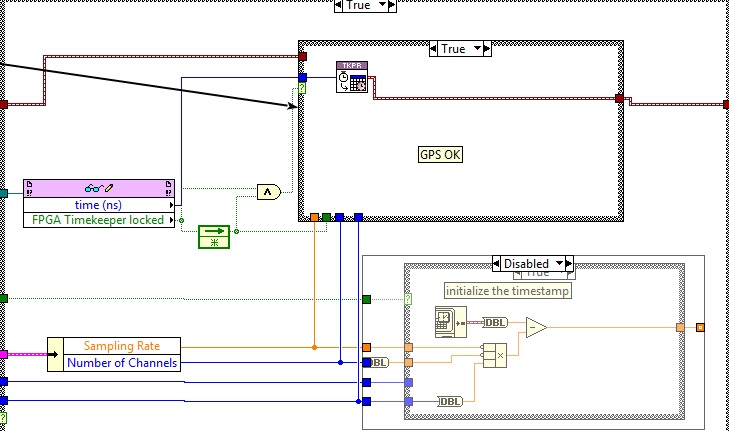

I have implemeneted the code from the Synchronize to GPS Timekeeper example to my existing FPGA applicaiton. Now before I start the acquisiton I just wait for valid GPS signal (FPGA Timekeeper Locked = TRUE) as shown on the picture bellow.

After that I continue with the acquisition on the FPGA side by using DMA FIFO as it is done in the example (Delta Sigma Contunous acquisition (pipelined)).

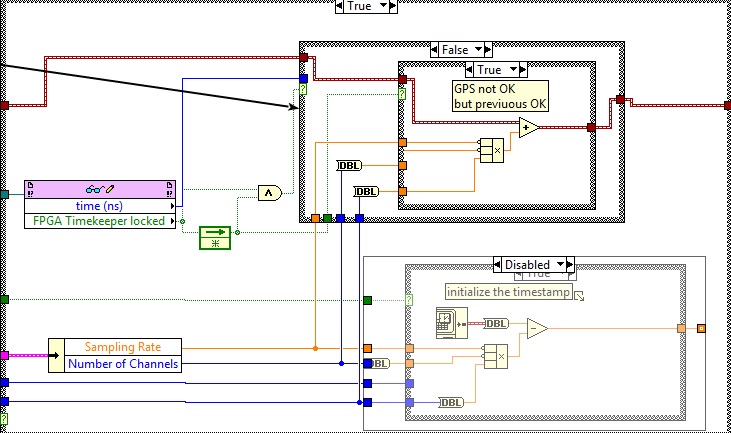

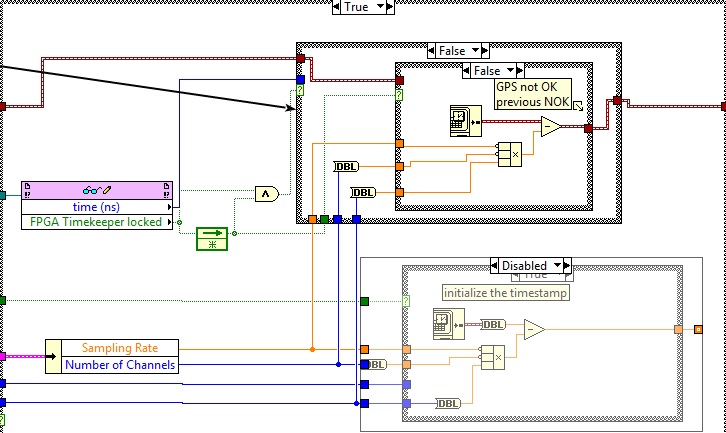

At my RT side similar to the example (Delta Sigma Contunous acquisition (pipelined)) I have modified the rwfm_AcqRead(Wfm)_ subvi (which is reading the data from the FIFO and builds the waveform) in order to read the time in ns form the Time keeper and convert that one to LabvIEW time in order to time stamp the data. Please see the below pictures for different use cases (valid and NOT valid GPS signal).

Please let me know what do you think of this implementation as my only means of testing the code will be on site directly where I will have limited resources.

Thanks again,

01-27-2016 04:33 PM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

Hi TinoMK,

What are you concerned with in this code? Are you focusing on the GPS valid / not valid cases, or the use of Timekeeper VIs in the FPGA and RT side?

Lauren

Applications Engineer

National Instruments

01-28-2016 05:36 AM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

Hi Lauren,

I just wanted your opinion on the implementation of the Timekeeper vi's on both FPGA and RT sides. I use GPS valid/not valid cases in order to take some actions in case of loosing GPS signal during the acquisition.

I assume that on the RT side I need to get GPS time (time(ns)) on every iteration, than convert that time to LV time and use that as time stamp. This way in case of non valid GPS time in one iteration I need to take the described actions in the following iterations in order to continie with valid acquisition and timestamping.

What do you think?

Thanks,

01-29-2016 03:25 PM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

Hi TinoMK,

Assuming that you've followed the Synchronize to GPS example on the FPGA side, then as far as I can tell the logic makes sense and seems like it will work. There are no immediate issues that stick out to me.

Lauren

Applications Engineer

National Instruments