- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

NI 9215/ cRIO 9037 multiple modules data acquisition and logging

Solved!11-15-2017 03:24 PM - edited 11-15-2017 03:45 PM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

Hi,

I am new to LabVIEW FPGA. I am using cRIO9037. My project is to acquire data for multiple analog modules NI9215. Sampling rate 2KHz. I used the examples to build the template. The example program which acquires data from 1 module (4ch) works well, however when I try to add on other modules (all the modules are NI9215), I am not able to figure out the changes that must be done. What changes should I make? Can I get a help over this?

Solved! Go to Solution.

11-15-2017 04:05 PM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

I cant open the VIs but from the picture I can see 8 channels over 2 modules on the FPGA, does this work OK?

In general, to add new modules, you need to add them to project under the FPGA, then you can drag the IO nodes into the block diagram.

The example you have seems to be multiplexing the data from multiple channels into the DMA FIFO to the RT (you feed them in one at a time, as this is the fast end, then on the RT you bulk read them as an array, then decimate it back into the channel data). this is the only wat to keep up in many situations.

Its worth noting that on the old CRIO systems there were only 3 DMA fifos, so heavy multiplexing in code is common. Depending on the application and data requirements, on newer targets you can get away with multiplexing less by splitting the load over more DMA channels.

11-15-2017 04:20 PM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

Thanks for your reply.

I have added the FPGA I/O modules by dragging and dropping them. My project in total has 5 modules (4ch each). I wanted to try acquiring data from the first two modules so that I can apply the same for the rest. However, I am not able to solve it and find where I had made a mistake.

The example works fine for 1 module (4ch each). I would like to have the same for the rest of the analog modules.

11-15-2017 04:37 PM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

I dont have 2017 installed, so I cant look at the VIs 😞

11-16-2017 08:33 AM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

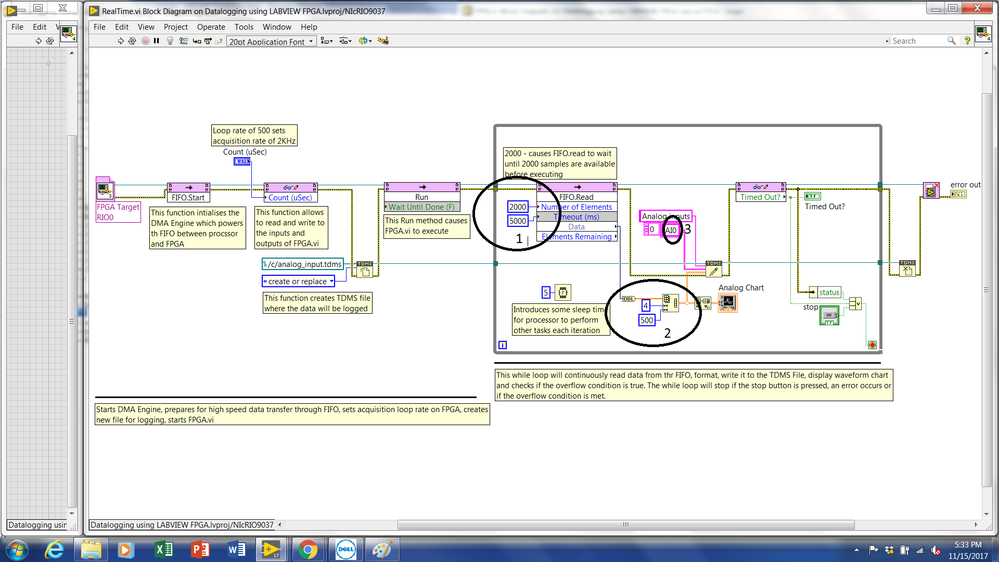

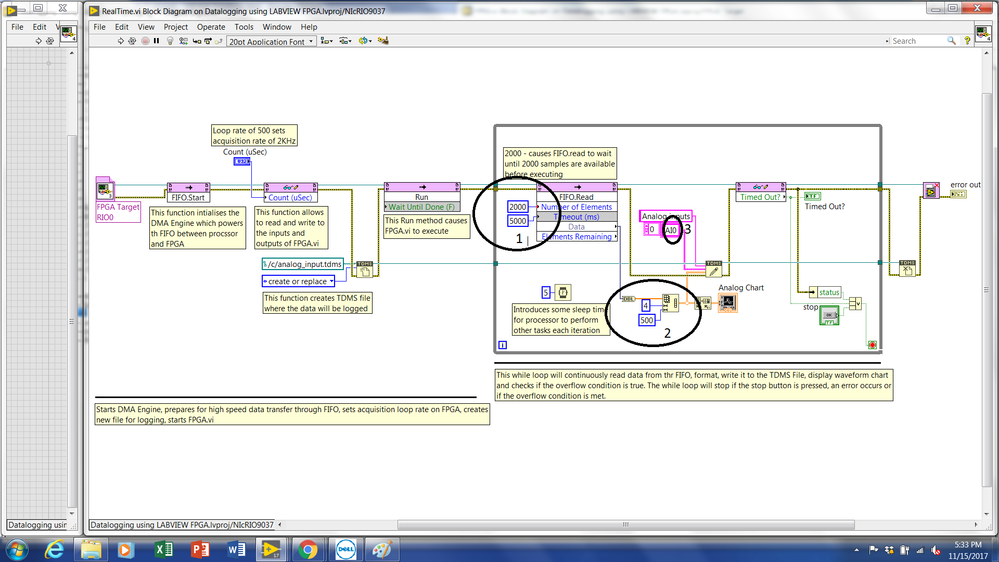

Oh!! If you could help with the screenshots - Attaching the screenshots of FPGA.vi and RT.vi.

11-16-2017 01:43 PM - edited 11-16-2017 01:44 PM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

OK, so at (1) you are allowing a wait of 5 seconds to have 2000 elements in the DMA FIFO sent from the FPGA.. This is OK as long as we change something else 🙂

At (2) We are grabbing 2000 elements from the FIFO and converting them to double precision float data.

These elements were multiplexed from the different channels in the FPGA, so the data goes like this

1st sample from MOD1\AI0

2nd from MOD1\AI1

3rd from MOD1\AI2

4th from MOD1\AI3

5th from MOD2\AI0

6th from MOD2\AI1

7th from MOD2\AI2

8th from MOD2\AI3

9th from MOD1\AI0 again

etc............... up to 2000

We need to decimate this back up into the correct channels. So we see at (2) that we reshape the array into 4 lots of 500 elements. This is bad for you since you want 8 lots of 250, because thats how you packed it into the FIFO on the FPGA end.

Should be simple enough to remedy by changing the 2 values.

At (3) there is an array, im guessing its just 4 elements with the channel names for the TDMS log files, you will need to add more to this so the array has 8 elements, one for each of the channels.

Hope thats clear but let me know if you're lost.

0xDEAD

11-16-2017 02:40 PM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

Hmmm. I typed out a reply to this and it has disappeared. 😞

11-16-2017 02:49 PM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

At (1) you are specifying that you want to read 2000 points from the DMA FIFO. You populated this in the FPGA from all 8 channels.

The order of elements who live in this array is:

mod1\ai0

mod1\ai1

mod1\ai2

mod1\ai3

mod2\ai0

mod2\ai1

mod2\ai2

mod2\ai3

mod1\ai0

mod1\ai1......... etc up to the 2000th element. Since this is how you packed them in on the FPGA.

However at (2) you reshape the array, essentially decimating the data back into "per channel" data from the interleaved data you created in the FPGA, thi is where the first problem is... You are reshaping it into 4 channels of 500 elements, wheras you the data actually is comprised of 8 channels of 250 points each.

An easy fix by changing them 2 values.

At (3) you have an array of channel names for the TDMS logging. This will only contain 4 channels, but you need it to contain 8 so your data get written to the correct place.

Hope this helps.

0xDEAD

PS. My first post was more in depth but the forum seems to have eat it. Any questions let me know.