- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

Labview FPGA Square Wave Inaccuracies

Solved!08-23-2017 07:52 AM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

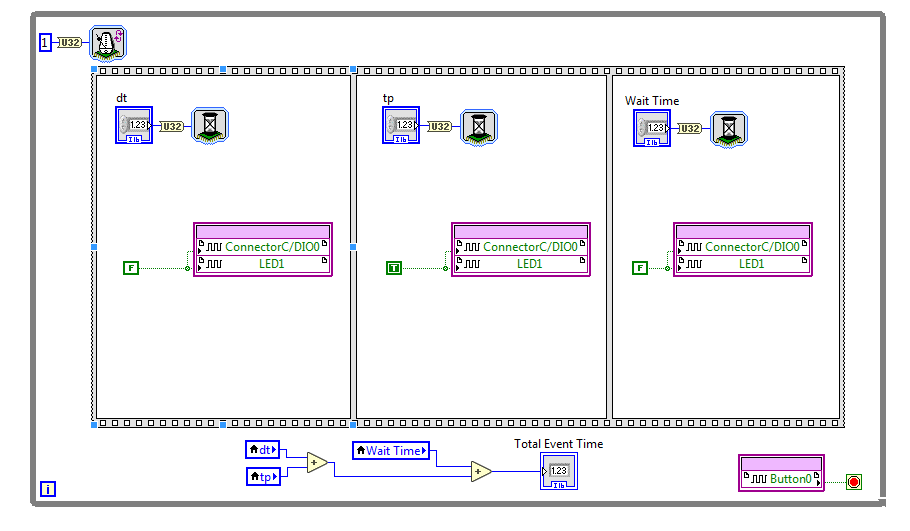

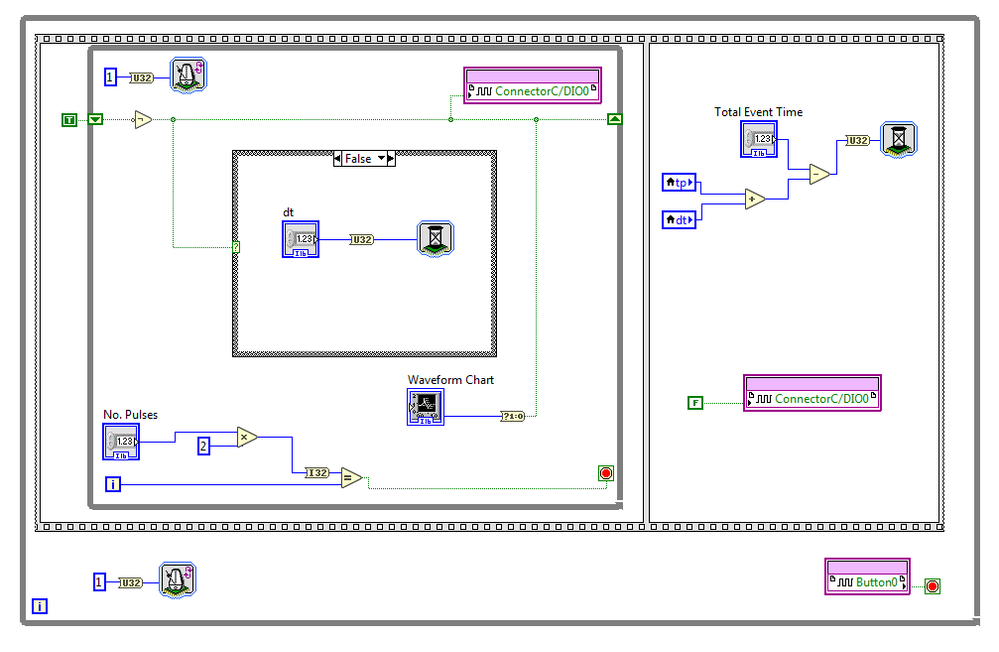

Hello, I am trying to create a high frequency square wave for a student project. The signal is to go to a digital output port of a myrio (1900) that will be used to trigger a MOSFET in a separate circuit, and I'd like to get the pulses down to as near 25 ns apart as possible (a single tick on the myrio's 40 MHz clock).

I have created a few different simple VIs that send alternating true/false values out to a DIO port of the myrio but as yet each has produced very irregular/inconsistent signals on a waveform chart, even at very low (~1 Hz) frequencies. The manual ones contain an extra wait period after the burst of pulses so that it can be more easily synchronised with other hardware (e.g. a camera shutter).

I was told that the FPGA should be very deterministic and that a consistent 25ns pulse is achievable, so I imagine I'm missing something in the coding. Is there a better approach or something obvious that I'm missing? Could this be due to a lingering dependence on software timing instead of the actual onboard clock (maybe because there's a waveform chart in there for example)?

I don't have access to an oscilloscope so I can't be sure of exactly what signal's actually being produced by the hardware. If I wire the output to the onboard LED of the myrio, or connect the DIO to an LED on breadboard, it appears to produce a consistent pulse when at low enough frequencies to be visible. This doesn't tell me much about what's happening at higher frequencies but it suggests that the odd readings on the waveform chart are probably erroneous, at least at low frequencies. Is my problem that I'm measuring the output through software or am I implementing the DIO/FPGA in the code incorrectly?

Any help or general advice would be greatly appreciated.

Thanks,

Max

Solved! Go to Solution.

08-23-2017 08:01 AM - edited 08-23-2017 08:02 AM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

Your assumptions are correct on the FPGA and base clock. I recommend checking the 1900 datasheet: http://www.ni.com/pdf/manuals/376047c.pdf (pages 21-22) on the DIO lines. I believe the myRIO (similar to cRIO) goes through a bus (from FPGA to I/O) which keeps it from running that quickly.

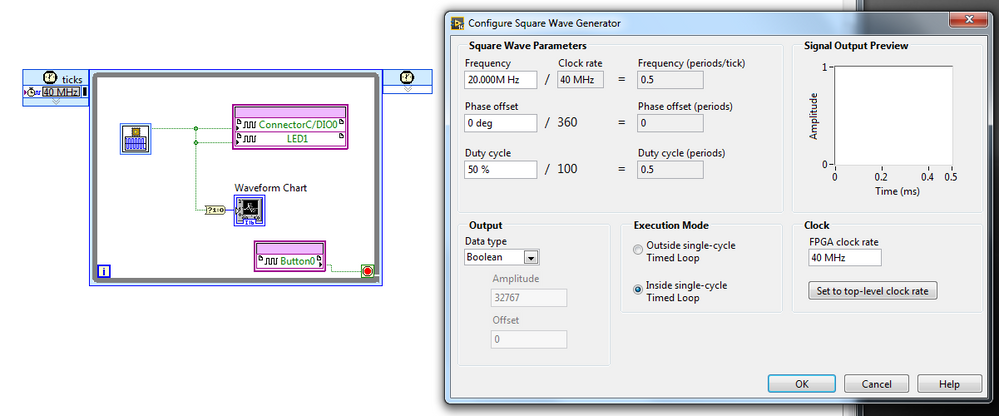

If that is not a case, your best bet is to review some DIO examples and to go with a Single Cycle Timed Loop (SCTL). Not sure which clock to run the SCTL, examples may help.

To test, you could loop back the output and input pins.

Certified LabVIEW Architect, Certified Professional Instructor

ALE Consultants

Introduction to LabVIEW FPGA for RF, Radar, and Electronic Warfare Applications

08-23-2017 08:50 AM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

Thanks for the feedback Terry. Ok, it looks do-able then, if not quite as quick as I'd like.

When you say loop back the output and input pins, does that mean wire two DIO ports together (physically) and write the true/false to one and then read the signal from the other? Would you use a waveform chart again to see that? How does it differ from what I've got already? Sorry I am pretty new to this

08-23-2017 08:57 AM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

I have learned not to trust charts on an FPGA front panel. Just use the SCTL approach. I am pretty sure those DIO can handle it.

There are only two ways to tell somebody thanks: Kudos and Marked Solutions

Unofficial Forum Rules and Guidelines

"Not that we are sufficient in ourselves to claim anything as coming from us, but our sufficiency is from God" - 2 Corinthians 3:5

08-23-2017 09:13 AM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

Is there a way I can monitor it, particularly fall and rise times? Or should I trust that a SCTL will produce the right thing/a decent pulse?

08-23-2017 10:04 AM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

@mFred11 wrote:

Is there a way I can monitor it, particularly fall and rise times?

For that, you need an oscilloscope.

There are only two ways to tell somebody thanks: Kudos and Marked Solutions

Unofficial Forum Rules and Guidelines

"Not that we are sufficient in ourselves to claim anything as coming from us, but our sufficiency is from God" - 2 Corinthians 3:5

08-23-2017 10:09 AM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

Ahh I suspected as much. Thanks crossrulz