- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

Is it possible to configure multiple peer-to-peer streams between PXIe-7858R and PXIe-6593?

02-28-2023 09:06 PM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

I'm new to peer-to-peer streaming between FPGA targets so please be gentle...

I have a PXIe-7858R (which serves as the writer for the peer-to-peer stream) and a PXIe-6593 (which serves as the reader for the peer-to-peer stream) in a 1095 chassis. I have successfully configured the stream between the 2 FPGA targets and can send/receive data.

I am curious if it's possible to configure 2 or parallel peer-to-peer streams between these 2 FPGA targets. I am trying to simulate having more traffic going between the PCIe switches so that I can see how much the latency of the peer-to-peer could be affected. When I add a 2nd stream, everything seems fine until I run the host VI. The stream says that it is enabled but when I monitor the stream status on the FPGA, both the writer and reader endpoints for the 2nd stream are unlinked.

TLDR:

Is it possible to have multiple writer and reader endpoints for a peer-to-peer stream on 1 FPGA target?

02-28-2023 11:03 PM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

@[dk] wrote:

I'm new to peer-to-peer streaming between FPGA targets so please be gentle...

I have a PXIe-7858R (which serves as the writer for the peer-to-peer stream) and a PXIe-6593 (which serves as the reader for the peer-to-peer stream) in a 1095 chassis. I have successfully configured the stream between the 2 FPGA targets and can send/receive data.

I am curious if it's possible to configure 2 or parallel peer-to-peer streams between these 2 FPGA targets. I am trying to simulate having more traffic going between the PCIe switches so that I can see how much the latency of the peer-to-peer could be affected. When I add a 2nd stream, everything seems fine until I run the host VI. The stream says that it is enabled but when I monitor the stream status on the FPGA, both the writer and reader endpoints for the 2nd stream are unlinked.

TLDR:

Is it possible to have multiple writer and reader endpoints for a peer-to-peer stream on 1 FPGA target?

Something seems off about how you are describing the P2P streams. A writer and a reader are made into a stream. Once they are joined you cannot use those writers and readers in another stream. You must have one and only one writer and reader for each stream. Makes sense? Am I correct in my assumption of what you say above?

Certified LabVIEW Architect, Certified Professional Instructor

ALE Consultants

Introduction to LabVIEW FPGA for RF, Radar, and Electronic Warfare Applications

02-28-2023 11:03 PM - edited 02-28-2023 11:37 PM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

@elainao wrote:

@[dk] wrote:

I'm new to peer-to-peer streaming between FPGA targets so please be gentle...

I have a PXIe-7858R (which serves as the writer for the peer-to-peer stream) and a PXIe-6593 (which serves as the reader for the peer-to-peer stream) in a 1095 chassis. I have successfully configured the stream between the 2 FPGA targets and can send/receive data.

I am curious if it's possible to configure 2 or parallel peer-to-peer streams between these 2 FPGA targets. I am trying to simulate having more traffic going between the PCIe switches so that I can see how much the latency of the peer-to-peer could be affected. When I add a 2nd stream, everything seems fine until I run the host VI. The stream says that it is enabled but when I monitor the stream status on the FPGA, both the writer and reader endpoints for the 2nd stream are unlinked.

TLDR:

Is it possible to have multiple writer and reader endpoints for a peer-to-peer stream on 1 FPGA target?

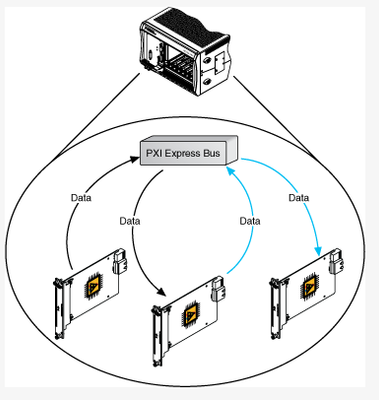

In the system depicted in Figure 1, a PXIe-5622 digitizer in a PXIe-1075 chassis uses peer-to-peer data streaming to send data directly to a PXIe-7966R FlexRIO FPGA module. The FPGA module then sends data to another FPGA module for additional processing. Because the chassis backplane switches provide direct links to the slots occupied by the modules, you do not need to transfer data through the host controller or use system resources such as the CPU or host memory.

Is this Spam? Maybe generated by Chat-GPT?!

Certified LabVIEW Architect, Certified Professional Instructor

ALE Consultants

Introduction to LabVIEW FPGA for RF, Radar, and Electronic Warfare Applications

03-01-2023 08:02 AM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

Ok yes, that does make sense. Only 1 writer and 1 reader per stream.

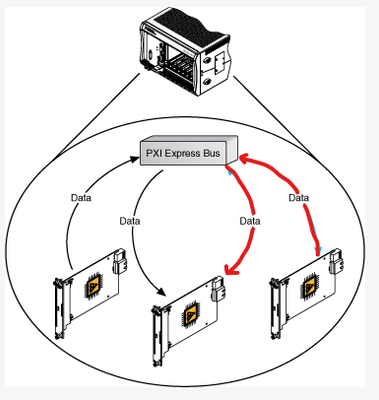

So now I'm curious about another scenario. Let's say I have 2 PXIe-7858R and 1 PXIe-6593 in a chassis. Can I set up a P2P stream between each 7858R and the 6593? So each 7858R would have a writer endpoint and the 6593 would have 4 reader endpoints.

In the P2P streaming documentation that I've found, the topology is always described as each FPGA target only having 1 reader and 1 writer.

Peer-to-Peer Data Streaming - Multiple FPGA Devices, Multiple Streams Topology - NI

Is something like this below possible?

03-01-2023 08:23 AM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

@[dk] wrote:

Ok yes, that does make sense. Only 1 writer and 1 reader per stream.

So now I'm curious about another scenario. Let's say I have 2 PXIe-7858R and 1 PXIe-6593 in a chassis. Can I set up a P2P stream between each 7858R and the 6593? So each 7858R would have a writer endpoint and the 6593 would have 4 reader endpoints.

In the P2P streaming documentation that I've found, the topology is always described as each FPGA target only having 1 reader and 1 writer.

Peer-to-Peer Data Streaming - Multiple FPGA Devices, Multiple Streams Topology - NI

Is something like this below possible?

This is possible with P2P. Good feedback re the P2P documentation.

Certified LabVIEW Architect, Certified Professional Instructor

ALE Consultants

Introduction to LabVIEW FPGA for RF, Radar, and Electronic Warfare Applications