- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

FIFO missing data

Solved!04-26-2019 04:16 AM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

Hello everyone!

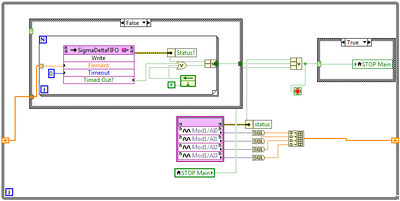

i'm currently acquiring data from two different kind of sensors using a cRIO9039 and labview 2016. Since i use both a NI9234 and NI9220, who have different clock rates, i need to use 2 FIFOs to pass data from my FPGA side to my RT side.

Both loops are written so they acquire data at 12.8kHz. In the SigmaDeltaFIFO i put 4 values each iteration, in the MEMS FIFO it's 32 values. In the RT loop i read out the data and decimate it back into the seperate measurements.

My RT system uses a Wait until next ms multiple function to execute every 20ms multiple. I played around with this value and the problem occurs more often at higher values (>50ms) and also more often when going to lower values (<5ms).

Now to my problem:

The Elements Remaining of the MEMS FIFO should always be a multiple of 32. During a 10 minute measurement i sometimes get a TimeOut error from this FIFO and have only 31 Elements Remaining. What could be the reason / solution?

This problem does not occur during every measurement, and it never occurs at the same time. Sometimes it happens after 30 seconds, sometimes after 9 minutes.

It would be great if any of you could help me with this problem.

Solved! Go to Solution.

04-26-2019 08:43 AM - edited 04-26-2019 08:47 AM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

I wouldn't put a wait in the read loop. Read as fast as possible, and let the TO of the read introduce a wait if it's idle.

The feedback node in that FIFO write loop probably isn't right. It will remember status from previous iterations, so an error of the 4th element will be remembered for the next 1st element. You probably want to use a shift register for that.

If there is an error, you're in trouble, and it will be impossible to recover anyway. Once multiple channels over a single FIFO are out of sync, there's no way for the reader to get back in sync.

04-26-2019 12:07 PM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

I'm neither a RT or FPGA savant, but you can try this on the RT side:

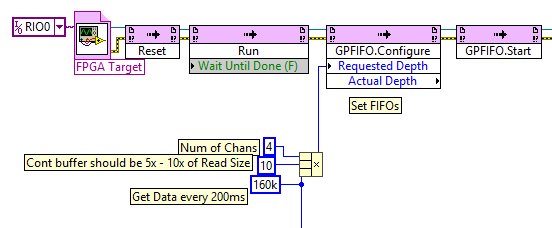

- Configure the depth of the FIFO; should be 5-10x times the read size.

- Read the buffer every 100-200ms; I used 200 ms in my application.

- So in your case, 12.8kHz, in 200ms, 2560 points, times 32 channels, make the depth 2560*32*10 = 819200

- Read 163840 elements every 200 ms.

Below are some images.

mcduff

05-04-2019 06:56 AM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

Okay, it's running smoothly now. I ran tests for a couplt of days under different settings and i haven't encountered this error yet! Thank you!