- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

Error of external clock for CLIP (with sbRIO 9651)

03-27-2019 07:45 AM - edited 03-27-2019 07:47 AM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

Hello everyone,

I´m using a FPGA Target (sbRIO 9651) to control a ADC (LTC2174) for data acquisition. Now I want to make a test, and see if there are Problems that the output data of the ADC are displayed in Labview.

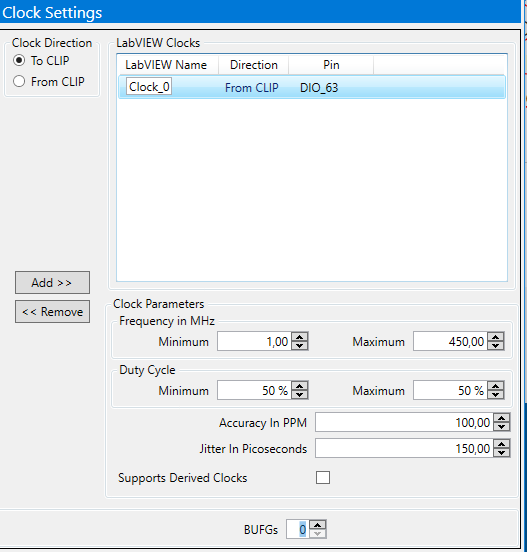

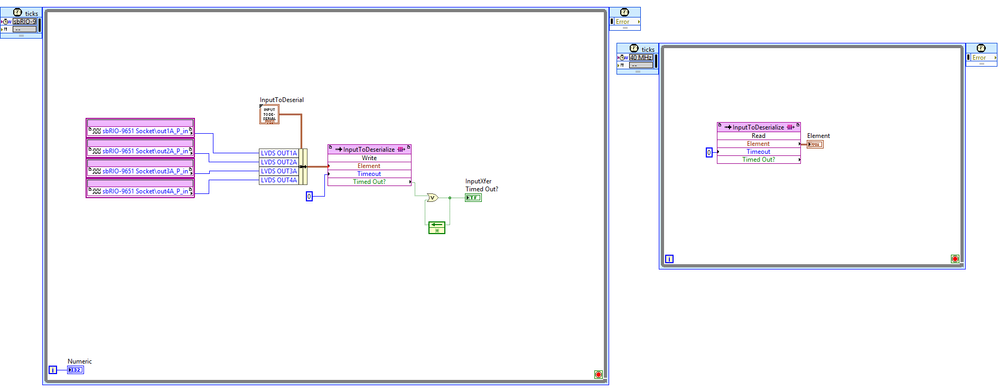

The data clock port DCO of the ADC is connected to the port DIO_63 of FPGA. I used 2 SCTL in Labview VI, one for data writing, and another for data reading. The clock source of SCTL for writing is DCO that was generated by sbRIO CLIP Generator. The clock source of SCTL for reading is Labview internal clock 40MHz.

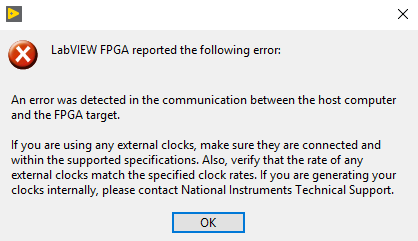

But when I compile this VI, there is a error (see picture). The problem seems to be on the external clock source.

I have attached below the error, clock setting and VI picture/file. Any help will be appreciated.

04-11-2019 09:28 AM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

Hi johnsnow34,

Regarding your error and screenshot, it seems the error is coming from the left SCTL, I would advise you to try to specify a fixed frequency for the input clock. From the datasheet this signal seems to be a fixed multiple of the Sampling Frequency so you can define the same value for the Maximum and Minimum value and update the generated clip. Also pay attention this signal is a differential signal.

Paolo_P

Certified TestStand Architect

Certified LabVIEW Architect

National Instruments France

04-14-2019 01:56 PM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

Hi Paolo_P,

I have tried a fixed frequency. But it doesn't work. I think that maybe the frequency of the clock too high for SCTL(400MHz).

04-15-2019 02:47 AM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

At which moment do you have this error message?

Running at 400Mhz seems pretty high frequency for LV FPGA implementation. Can you elaborate more why do you need this SCTL running at this frequency?

Paolo_P

Certified TestStand Architect

Certified LabVIEW Architect

National Instruments France

04-15-2019 03:26 PM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

Hi Paolo_P,

400Mhz is the frequency of ADCs bit clock. I want this clock as the source clock of acquisiton SCTL. Now I know that is not right. I shouldn't use DCO directly.

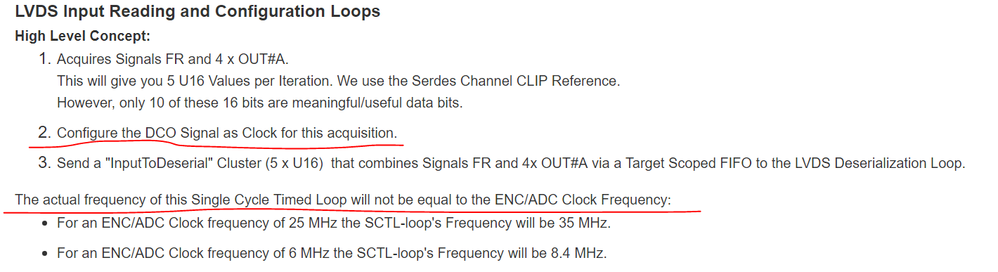

I refer to this example to design: https://forums.ni.com/t5/Example-Program-Drafts/Communicating-with-an-ADC-via-an-NI-6587-FlexRIO-Ada...

It was said in the example that the frequency for this SCTL should be a clock deried from DCO.

The FPGA hardware in the example is NI 6587, which has a STROBE port for incoming DCO. But my hardware is sbRIO 9651, and the DCO is connected with DIO_63 of sbRIO 9651. I tried to use one MMCM in CLIP Generator for DCO, but there is a LOC error:

ERROR: [DRC UCIO-1] Unconstrained Logical Port: 2 out of 184 logical ports have no user assigned specific location constraint (LOC)....Problem ports: aDio[63], and aDio_n[63].

How can I use a slower clock derived from DCO for SCTL?

- Tags:

- LabVIEW

04-18-2019 12:32 PM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

This example is really intersting. It use a programmable oscillator to specify the onboard clock which is divided by 5 inside the CLIP.

As far as I know there is no such a component for the SOM.

I didn't realized but if you want to import an external clock, the direction I'm seeing on your first post is not correct, for importing a clock you need to choose "From CLIP" option

I've also observed in the CLIP Generator that the DIO_63 is single-region clock capable. Have you just tried DIO_62 as a simple test, I'm not familiar with this error, but it worth to test it because in case of doubts, it is advised to use a mult-clock capable.

Paolo_P

Certified TestStand Architect

Certified LabVIEW Architect

National Instruments France

04-23-2019 04:02 PM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

Hi Paolo_P,

Thanks for your reply. The problem was solved. I should set DIO_63 as lvds_25. Because the external clock port is lvds_25. I also seleted 'supports derived clocks' and a divided clock from external clock(100Mhz) for SCTL worked fine.