- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

Component Level IP: Generate and Check Syntax Error

Solved!10-07-2016 03:55 AM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

I tried to create a component level IP for my myRio device. I encountered this problem:

Extracting top-level synthesis file information. Please wait... Processing files... Vivado Simulator 2014.4 Copyright 1986-1999, 2001-2014 Xilinx, Inc. All Rights Reserved. Running: C:/NIFPGA/programs/Vivado2014_4/patches/AR62969/vivado/bin/unwrapped/win32.o/xelab.exe xil_defaultlib.conf3B887A0FF22442ACAD7559670A4D090A -L xil_defaultlib -L unisim -L unimacro -L xilinxcorelib -L secureip -snapshot top -dll -prj clipsyn.prj Multi-threading is on. Using 6 slave threads. Determining compilation order of HDL files. INFO: [VRFC 10-163] Analyzing VHDL file "C:/NIFPGA/iptemp/clip6BEF358BFCFF45AD8C68F5AB63F88A19/top.vhd" into library xil_defaultlib INFO: [VRFC 10-307] analyzing entity top INFO: [VRFC 10-163] Analyzing VHDL file "C:/NIFPGA/iptemp/clip6BEF358BFCFF45AD8C68F5AB63F88A19/clock_div.vhd" into library xil_defaultlib INFO: [VRFC 10-307] analyzing entity clock_div INFO: [VRFC 10-163] Analyzing VHDL file "C:/NIFPGA/iptemp/clip6BEF358BFCFF45AD8C68F5AB63F88A19/pwmbuffer.vhd" into library xil_defaultlib INFO: [VRFC 10-307] analyzing entity pwmBuffer Starting static elaboration Completed static elaboration Starting simulation data flow analysis Completed simulation data flow analysis Time Resolution for simulation is 1ps Compiling package std.standard Compiling package ieee.std_logic_1164 Compiling package ieee.numeric_std Compiling architecture behavioral of entity xil_defaultlib.clock_div [\clock_div(40000000,400000)\] Compiling architecture behavioral of entity xil_defaultlib.pwmBuffer [pwmbuffer_default] Compiling architecture behavioral of entity xil_defaultlib.top [top] gcc.exe: Internal error: Aborted (program collect2) Please submit a full bug report. See <URL:http://www.mingw.org/bugs.shtml> for instructions. Fix the above error and check syntax again.

I have labview 2015 and vivado 2014.4 running on windows 8.1. Thank you in advance.

Solved! Go to Solution.

10-08-2016

04:14 AM

- last edited on

12-19-2024

03:09 PM

by

![]() Content Cleaner

Content Cleaner

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

Hello,

This is a strange error, I didn't realise gcc was actually used in the Xilinx compilation process. But it appears this is where the error is occurring. I would be curious as to whether this is a compiler corruption, missing files or whether this is specifically with your CLIP code.

Have you been able to compile FPGA code previously? If so, what is the CLIP code you have created and are trying to use? Is this running in an IP node or CLIP configured under FPGA Target -> Properties -> Component Level IP?

If you use the Compile Cloud, I would be curious as to whether you receive the same error, (this would narrow down whether it is the compiler or not). If you do not have SSP, you could sign up for 90 days free trial just to give it a quick run:

https://users.niwsc.com/compilecloud/

My next thought (probably the actual answer) is that you have the wrong Xilinx Compilation Tools installed. If you review the below linked document you should find that myRIO requires the ISE Compilation Tools, not Vivado:

Based on your version of LabVIEW, I would recommend to download and install the below Tools:

Please note: I generally always recommend to use the cloud service to avoid needing to figure out which tool to install, as well as the added benefit of compiling on a server dedicated and built for the task. Although this is only really necessary for very very large compilations.

Best regards,

Ed

10-14-2016 01:04 AM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

Thank you for your response.

I solved the problem. It is apparently caused by minGW installed with vivado 14.4 that doesn't work with windows 8. So, I replaced the minGW on vivado 14.4 folder with the newest version of minGW.

05-11-2017 04:42 AM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

Hi I'm Having the same problem with LB2016 and Vivado 2015.5.

Where i can find Mingw?

regards

05-11-2017 04:48 AM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

05-11-2017 05:16 AM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

i've download and repalced the folder 5.0.0

now i've dthis problem :

Extracting top-level synthesis file information. Please wait...

Processing files...

Assembler messages:

Error: can't open xsim.dir/DemoClipAdder/obj/xsim_1.win32.as for reading: No such file or directory

Assembler messages:

Error: can't open xsim.dir/DemoClipAdder/obj/xsim_0.win32.as for reading: No such file or directory

02-07-2018 09:13 PM - edited 02-07-2018 09:15 PM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

I recently had the same problem.

The fix was to copy the new MinGW files over the top of the existing ones, and choose "Replace" where the same files exist. Removing the existing contents and replacing with the new version doesn't seem to work - so there must be some files in there that need to stay put.

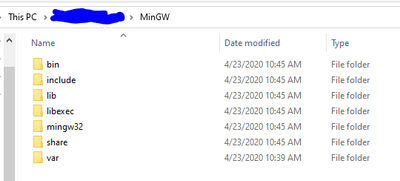

The folder I replaced was "C:\NIFPGA\programs\Vivado2014_4\tps\mingw\5.0.0\win32.o\nt" for LabVIEW 2015 Vivado tools. Only performed a basic install of the "mingw32-base" package. IP Integration now working fine.

Hope this helps.

04-15-2018 07:02 PM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

@Claytoid wrote:

I recently had the same problem.

The fix was to copy the new MinGW files over the top of the existing ones, and choose "Replace" where the same files exist. Removing the existing contents and replacing with the new version doesn't seem to work - so there must be some files in there that need to stay put.

The folder I replaced was "C:\NIFPGA\programs\Vivado2014_4\tps\mingw\5.0.0\win32.o\nt" for LabVIEW 2015 Vivado tools. Only performed a basic install of the "mingw32-base" package. IP Integration now working fine.

Hope this helps.

I confirm that this method also works for Windows 10 64-bit ver 1709 & LabVIEW 2017 SP1 & Xilinx Compilation Tools for Vivado 2015.4!

04-16-2018 01:48 AM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

Thanks

lm

04-23-2020 09:54 AM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

Sorry for re-opening an old topic. My work PC was refreshed to Win 10, and I am responsible for managing a LabVIEW FPGA 2017 SP1 design.

The target device is the PXIe-7971R FlexRIO card, and when updating the Socket CLIP, I have run into this same problem. I've attempted to follow the solution provided:

1. Get the latest MinGW installer from their website.

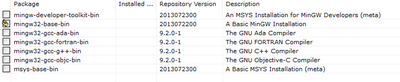

2. Install "mingw32-base-bin (shown below) by checking the box, and applying changes.

3) Copied all of the directories as shown from c:/MinGW

to the following folder, overwriting all conflicting files.

4) Open LabVIEW 2017 SP1.

5) Re-open my project

6) Open Properties for my FPGA, and choose "Component Level IP"

7) Create a new CLIP - follow the usual config for my system along with adding the .vhd and .xdc files.

Receive Error:

Error 1097 occurred at Call Library Function Node in niFpgaIPINodeGetPortsInfo.vi:2590001->niFPGA_ClipGenerator_DoFuse.vi->niFPGA_ClipGenerator_WizardPage3.vi

Possible reason(s):

LabVIEW: An exception occurred within the external code called by a Call Library Function Node. The exception might have corrupted the LabVIEW memory. Save any work to a new location and restart LabVIEW.

Have I skipped any steps? Has anyone seen this similar issue when attempting LVFPGA 2017 + Vivado 2015.4 + Win 10?

Thanks in Advance,

J