- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

i go a strange behaviour from PXI 7830R digital output, two of digital output channel goes high when i stop the code...

04-01-2010 09:16 AM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

hai friends,

I am using PXI 7830R for source 3.4 v from connector 1. when i am executing the code, i am able to control the digital output, but when i stop the execution, channel 3 and 5 output automatically goes to high. how to troubleshoot this.....please help me.....

04-02-2010 10:13 AM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

Have you tried adding shut-down code to the end of your VI that manually sets all DIO channels low? When you stop a VI the DIO should stay at the state in which the VI ends. How are you stopping the VI? Do you just have a stop button the ends a loop or are you force aborting it? Also are you stopping the host VI or the FPGA VI?

PS. Duplicate post here

04-05-2010 01:55 PM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

Thank you Mr.David,

i am using abort function in RT to stop the FPGA code.... in my code, i can set active high or active low to 3rd and 5th channel....but when i stop the code from RT then the 3rd and 5th channel goes to active high even in previous state these are in active low...when i reboot the RT, these channels are in active high....what is the problem...

04-06-2010 02:40 PM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

When there is no VI running on the FPGA, DIO lines are set to high impedance. Depending on what you have the line connected to, you can see different results. There are two methods I would suggest to avoid this:

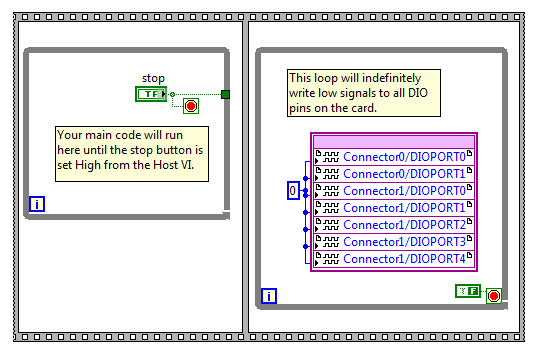

Instead of aborting your code, stop your FPGA loop with a boolean control. Then after your while loop ends, have another endless loop that will always write false to the DIO pins. See the image for an example:

Alternately, you can use a pull down resistor external to the FPGA card that will always set the pin to be low if it's in a high impedance state.

Similar to my first suggestion, you can also set a VI to run at startup in order to control the power on state of the device. See the following KB for more information on this:

http://digital.ni.com/public.nsf/allkb/CB2F146DB6B56D29862572640073B57D?OpenDocument