- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

SIT cRIO 9025

08-14-2012 06:01 AM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

Hello everyone,

i have a question about the real time control design.

my harware's are:

NI cRIO 9025

chasis cRIO 9112

Analog input NI 9215

Analog output NI 9264

I have a Matlab model. I use a (SIT) simulation interface toolkit to obtain .dll file

than open blank .vi mapping SIT connection manager, select .dll and mapping with the graps and indicators.

But in the Hardeware I/O selection when I am try to map hardware, there is only show the ip number of my device 169.254.84.198

I cant see the any analog input and output ports therefore i cant map the Hardware I/O with my Matlab model.

Is there any problem with my procedure.

regards

Sinan B.

08-15-2012 12:28 PM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

Hi Sinan,

Using SIT with a cRIO target is a little more complicated then that. For one thing, you cannot run DLLs on VxWorks; you have to generate a .out file. For another, to interface with the hardware i/o through the fpga you must create a custom bitfile in order to create a .out file that will work for your setup.

This tutorial takes you through all of the steps necessary to get this model running on your cRIO with proper mapping: http://www.ni.com/white-paper/11654/en

Its specific to the sinewave example but you can use the steps it goes through to implement your own model.

Generally, we recommend a newer product, VeriStand, for doing this sort of thing if you're interested. It does everything that SIT does and much more.

08-16-2012 05:21 AM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

Hello Alisha P

How to generate .out file. In matlab there is nidll.tlc but there is no nidll_vxworks.tlc.

How can i add it to matlab to generate.

Regards.

Sinan Başaran-GYTE

08-16-2012 09:29 AM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

Hey Sinan,

Sounds like VxWorks support has not been enabled.

Did you try looking at the info in Step 1 under "Compiling the Model..." in the tutorial I referenced?

This references this Knowledge Base article: http://digital.ni.com/public.nsf/allkb/A564E382D31ABFCA862574CE006B228D

Have you followed the steps in the attached readme?

Getting your model to run on cRIO with SIT has a number of steps (as you can see in the tutorial). Each one must be followed carefully in order for it to work.

Good luck!

09-03-2012 08:13 AM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

Hello again.

i finally compile and generate the .out file than press the play button. 🙂

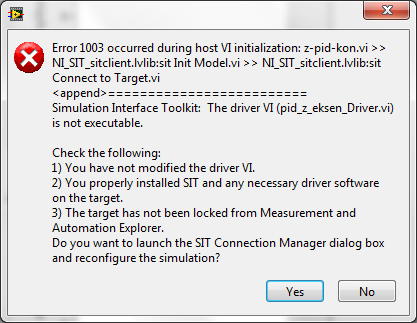

But there is an error dialog box

is there any idea about this error?.

Regards.

Sinan Başaran-GYTE

09-04-2012 09:15 AM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

Hi Sinan,

Have you been able to rule out the troubleshooting suggestions in the error message?

Do you have SIT and NI-VISA installed on the cRIO?

In the SIT Connection manager were you able to map the I/O to your hardware?

Do you have a solid connection with the target?

Are you able to run an example model - like the example Sine wave model?

09-10-2012 05:16 AM - edited 09-10-2012 05:17 AM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

I do all of them.

and i cant run the example model. it gave the same error.

09-11-2012 12:10 PM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

Hi Sinan,

Were you able to develop a custom FPGA VI for your 9025? This step can be tricky.

Can you post screenshots of the software installed on your cRIO and the series of dialog boxes in the SIT Connection Manager? Perhaps, post your FPGA VI so I can check if it's been customized appropriately.

09-13-2012 07:07 AM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

Hello Alisha P;

I upload my sit Example Sinewave Model. can you look at these, is there anything wrong?

09-14-2012 01:27 PM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

Hi Sinan,

What you have looks good. However, you have not included a custom FPGA bitfile (at least, I could not find one). Have you created the necessary bitfile as instructed in the linked tutorial?