- Document History

- Subscribe to RSS Feed

- Mark as New

- Mark as Read

- Bookmark

- Subscribe

- Printer Friendly Page

- Report to a Moderator

- Subscribe to RSS Feed

- Mark as New

- Mark as Read

- Bookmark

- Subscribe

- Printer Friendly Page

- Report to a Moderator

NI VeriStand Add-On: FPGA XML Builder Node

NI VeriStand Add-on: FPGA XML Builder Node

![]()

Overview

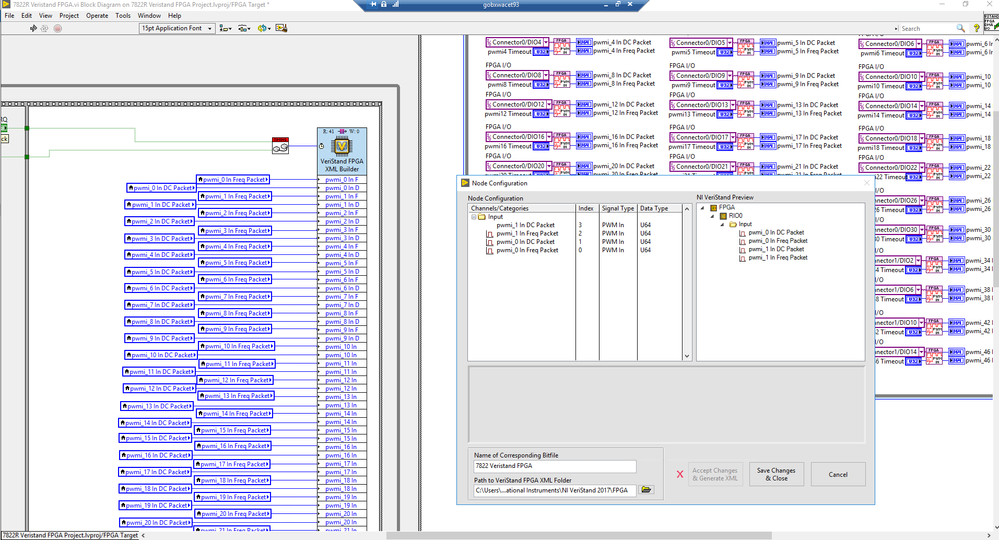

The VeriStand FPGA XML Builder add-on allows users to simplify FPGA VIs being developed for use with NI VeriStand. Traditionally, when creating an FPGA VI for use with NI VeriStand, the user had to bit pack all of the inputs and outputs of the system, as well as create the .fpgaconfig XML file that described the bitfile. The VeriStand FPGA XML Builder Node is a configuration based node which allows the user to specify channels to be sent and received from VeriStand, configure those channels, then automatically generate the necessary XML file for VeriStand. The node then internally handles the bitpacking of the channels and sends/receives the necessary packets using the DMA FIFOs to VeriStand.

Instructions for Use

After installing the VeriStand FPGA XML Builder node, and used in conjunction with the NI VeriStand FPGA-Based I/O Interface Tools, users can easily create FPGA VIs for use with NI VeriStand. You can add the node to the template's block diagram from the NI VeriStand FPGA Support » FPGA XML palette when in the FPGA context. Then expand the node for the number of I/O you'll be communicating with, configure your channels, and generate the XML configuration file.

A more detailed walk-through of implementing the FPGA XML Builder node is attached to this document.

Installing the VeriStand FPGA XML Builder Node

To install the FPGA XML Builder Node, complete the following steps:

VeriStand 2013 SP1

- Download and install the attached VIPM Package.

Veristand 2013 & VeriStand 2014+

- Ensure LabVIEW is closed

- Download the attached "Config File.zip" for your version of VeriStand. Unzip the folder and place the LabVIEW.exe.config file in the same directory as your LabVIEW.exe on disk. For most users, this directory will be at C:\Program Files (x86)\National Instruments\LabVIEW 20XX.

- Download and install the attached VIPM Package.

- After VIPM finishes, the LabVIEW.exe.config file can be deleted

Add-on Requirements to Run the FPGA XML Builder Node

All attempts have been made to provide an add-on compatible with the NI VeriStand shipping examples. The nature of some add-ons requires additional software or hardware to function.

Software

This add-on was created for use with NI VeriStand 2013+. To use this add-on you must have the following software installed:

- NI VeriStand 2013+

- LabVIEW 2013+

- NI-RIO

- NI VeriStand FPGA-Based I/O Interface Tools

Examples

This Add-On provides examples for implementing the node. After installation, these examples can be found at:

<LabVIEW>\examples\NI VeriStand Add-On-FPGA XML Builder Node

Known Issues

- After installing the VI Package, clicking on "Show in Palettes" will result in an error from VIPM of "We're sorry. VIPM could not locate the palette item." This occurs because this add-on is added to a palette in the FPGA context and VIPM searches only the My Computer context. If you create a VI under an FPGA target then you can navigate to the node on the NI VeriStand FPGA Support » FPGA XML palette.

- Having multiple channels/categories in the node with the same name will cause glyphs in the LabVIEW tree (in the configuration window, after double clicking on the node) to be incorrectly displayed. This also affects the ability to rename the duplicate channel, that doesn't display a glyph, from the subpanel "name" control in the configuration window. The work-around is to use unique names for all channels and categories. Further information regarding this known issue can be found here.

- Based on how the node is initialized and added to the palettes, the default value for the "Path to VeriStand FPGA XML Folder" (when configuring the node) will always default to the LabVIEW 2013 path. So, if you're using the node with LabVIEW 2014, you'll need to make sure you specify the location where you want the XML file to be created. Otherwise, it will try and create the XML file in the 2013 location and you will receive an error.

- The current default value for all channel types is 1. This works well for PWM, FXP, and DIO channels but you will need to enter the correct scale for any integer channels.

- Having channels of only the "Boolean" data type will cause an error when selecting "Accept and Generate XML" in the configuration screen. Workaround: Add at least one numeric channel.

- Having more than 64 output channels of type "Boolean" will result in a scripting error within the node and a broken run arrow. Workaround Option #1: Send your remaining booleans down as individual U8's and perform a !=0 comparison to get a boolean result back. Workaround Option #2: Locate the code generated by the node (see the "Instructions for Use" PDF), fix the wiring, manually paste it into your application, and basically create the bitfile the low level way without this node. Workaround Option #3: Use a model within the system definition to combine your booleans into a numeric, send that down to the FPGA, then re-convert back to an array of booleans on the FPGA.

Version History

1.1.2

- Bug - Fixed bug with XML generation on non-English operating systems where a comma is used instead of a period for the decimal mark (reported by forum user)

- Note - The source for this build now uses the VeriStand 2013 SP1 .NET assemblies. While this does not affect compatibility or supported versions, it will change the steps and files required to install/upgrade the add-on. Please see the installation instructions section above and download the new .NET configuration file if using a version other than VeriStand 2013 SP1.

1.1.1

- Feature - The node now copies the scripted code it creates into a VI called "VeriStand FPGA XML Scripted Code.vi" and saves the VI in the LabVIEW Data directory.

- Bug - Fixed a bug with packing of FXP inputs of 16 bits or less (reported by forum user)

1.1.0

- Feature - Added support for LabVIEW 2014 & VeriStand 2014

- Feature - Optimized reading from the DMA_Write DMA by unrolling the For Loop that performed the read (reduces FPGA fabric used)

- Bug - Fixed a bug with hard coded paths (reported by forum user).

- Bug - Fixed a bug with the default value for Scale (reported by forum user). Default value for Scale is now 1 instead of 0.

1.0.1

- Feature - Increased the maximum number of inputs/outputs to the node (number of rows that can be dragged down) to 500.

1.0.0

- Initial Release

Support and Contact

This add-on is provided "as is" and is not officially supported by National Instruments.

If you encounter a problem with this add-on, or if you have suggestions for a future revision, please post to the forum for this add-on here: VeriStand FPGA XML Builder Node Feedback Forum. You must use this feedback forum for support. Do not call National Instruments for support for this add-on.

National Instruments does not support this code or guarantee its quality in any way. THIS EXAMPLE PROGRAM IS PROVIDED "AS IS" WITHOUT WARRANTY OF ANY KIND AND SUBJECT TO CERTAIN RESTRICTIONS AS MORE SPECIFICALLY SET FORTH IN NI.COM'S TERMS OF USE (http://ni.com/legal/termsofuse/unitedstates/us/).

- Mark as Read

- Mark as New

- Bookmark

- Permalink

- Report to a Moderator

A very useful add-on. Well done!

- Mark as Read

- Mark as New

- Bookmark

- Permalink

- Report to a Moderator

Went from nothing to finished FPGA VI and XML file in half an hour. Really great!

- Mark as Read

- Mark as New

- Bookmark

- Permalink

- Report to a Moderator

Hello I have a question regarding this addon.

I tried to install the addon to LabVIEW 2013 but the VIPM said the add on doesn't support the LV 2013.

The HILS system is running now so I don't want to upgread to LV 2014 or 2015 for now.

Is there any way to install the addon to LV 2013 ?

Thank you for your help.

Best regards,

Tomomitsu Wakugawa

FSE @ NI Japan

- Mark as Read

- Mark as New

- Bookmark

- Permalink

- Report to a Moderator

The package is compatible with LabVIEW 2013, but you likely need to install VIPM 2014 since the package was built with VIPM 2014. You're likely encountering the issue described here.

- Mark as Read

- Mark as New

- Bookmark

- Permalink

- Report to a Moderator

Hello Ryan

Thank you for the quick response. I will try to upgrade VIPM.

thanks for your help.

Regards,

Tomomitsu Wakugawa

- Mark as Read

- Mark as New

- Bookmark

- Permalink

- Report to a Moderator

This add-on is very useful but I found a problem.

It seems that splitting the data written by VeriStand is incorrect.

I want to send reproducible code to you.

Would you contact me by e-mail?

Thanks,

Yusuke Tochigi

- Mark as Read

- Mark as New

- Bookmark

- Permalink

- Report to a Moderator

Regarding Known Issue #5 - I believe I see the bug, but am unsure of the correct solution. It appears that, when selecting a numeric as an output, you set a Boolean to true in the "Create Index Array for Numeric Output" VI. If there are no numerics, this Boolean is set to false. Then, in the "Create and Wire Index for Unpack Booleans" VI, you use that previous Boolean output as an input named Add Chunk? This appears to choose whether to create a new feedback node or use one previously created. Perhaps this would work if the condition on that case structure was "If Add Chunk? is TRUE OR the feedback node refs array is EMPTY, then create a new feedback node".

Thoughts?

- Mark as Read

- Mark as New

- Bookmark

- Permalink

- Report to a Moderator

Hello,

When I double click on the node I only see the first 4 signals that are mapped. All I am doing is measuring PWM Input frequency and Duty cycle which are 64 but unsigned numeric. Only the first 4 shows up and I get the error codes 1055 and 1136 as shown below. I have also attached a snapshot of the code. Any suggestions?

Date: 3/18/2019

Time: 2:16 PM

Error: 1055

Error Source: Property Node in Double Click Tree Read Tree subVI.vi->Node Configuration.vi->FPGA XML.xnode:OnDoubleClick2.vi->FPGA XML.xnode:OnDoubleClick2.vi.ProxyCaller

Date: 3/18/2019

Time: 2:19 PM

Error: 1136

Error Source: Property Node (arg 1) in Double Click Build Tree SubVI.vi->Node Configuration.vi->FPGA XML.xnode:OnDoubleClick2.vi->FPGA XML.xnode:OnDoubleClick2.vi.ProxyCaller

<APPEND>

Property Name: <b>Active Item:Tag</b>

Thanks

- Mark as Read

- Mark as New

- Bookmark

- Permalink

- Report to a Moderator

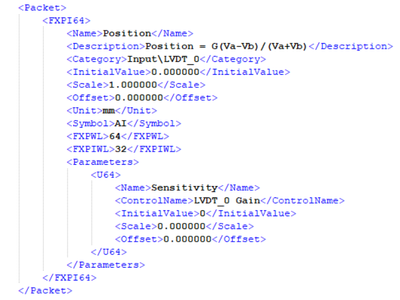

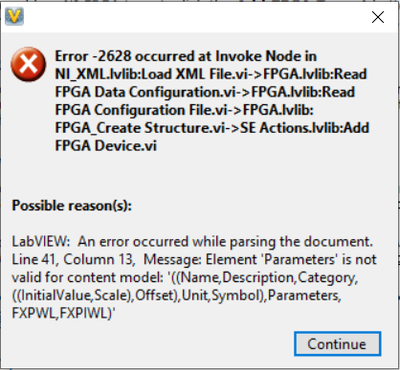

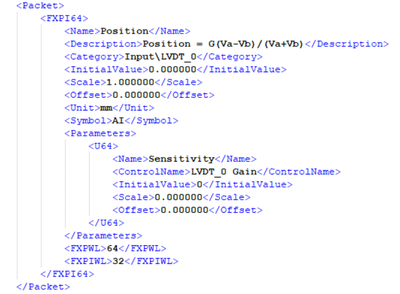

When adding a parameter to an FXP channel, the XML builder node inserts the parameter section after the <FXPWL> and <FXPIWL> sections in the .fpgaconfig file as shown.

When selecting the .fpgaconfig file in the System Explorer, you will receive the following Error -2628.

Workaround: Manually place the parameters section <Parameters> ahead of <FXPWL> and <FXPIWL> sections in the .fpgaconfig file as shown.

- Mark as Read

- Mark as New

- Bookmark

- Permalink

- Report to a Moderator

Hello, I have a 1055 error when I tried to generate the xml

Date: 06/08/2024

Time: 13:09

Error: 1055

Error Source: Invoke Node in Create and Wire Output DMA and Loop.vi->XNode_BuildAction.vi->FPGA XML.xnode:GenerateCode.vi:6040001->FPGA XML.xnode:GenerateCode.vi.ProxyCaller

this is my code: my_pxie_7846r_io FPGA.vi

Thank you