- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

Help with new component

03-23-2011 02:23 PM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

Hi

We are using the ALD1106 and the ALD1107 MOSFET array chips to learn about current mirrors and differential amp.

The chip has one pin for the bulk, and I can't get correct configuration to create the chip.

We've got the SPICE parameters from ALD in one *.lib file.

I've created the ALD1106 and it got problems...

Any idea how can I make them both work?

Thanks

P.S.. I've attached the *.lib as txt file and the chip model.

05-02-2011 10:55 AM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

Hi,

Can you please explain what problem you got?

Here is also a great tutorial on how to creat a new component.

http://zone.ni.com/devzone/cda/tut/p/id/3173

Regards,

Leila Feyz,

National Instruments

05-08-2011 11:56 AM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

I've tried to follow the tutorial and I've failed to create the chip.

I think that my big problem is that I don't understand the SPICE param. that I got.

And what to do with common pins. Do I need to connect them to the same pin? Do I need to omit them (to create 3 pin FET)?

Thanks

Moses

05-10-2011 09:19 AM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

Hi Moses,

A .lib file is a library, it has multiple SPICE models in the same file and you have to copy only the model you want to simulate and create a component from that. Here are the models you mentioned:

This is the 1106 model:

National Instruments

07-17-2011 02:54 AM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

I did so, and the result is an error...

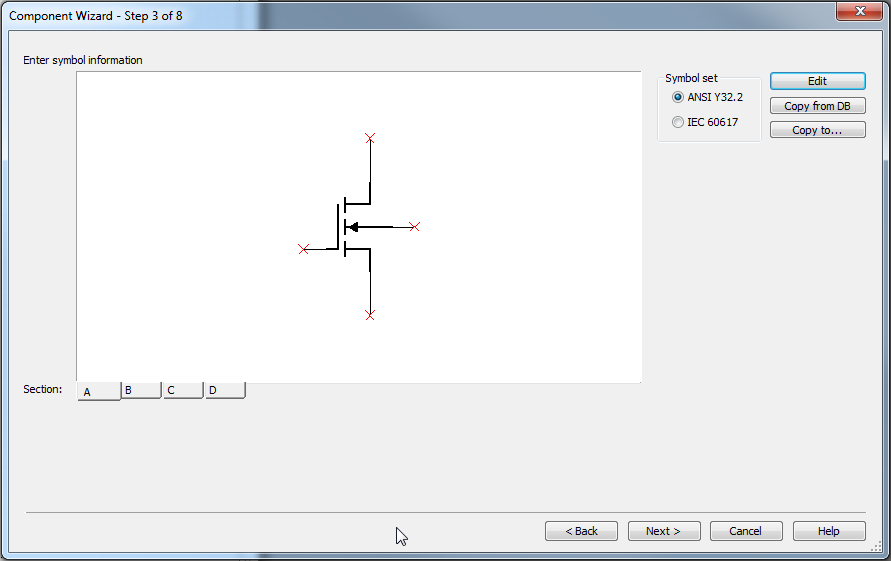

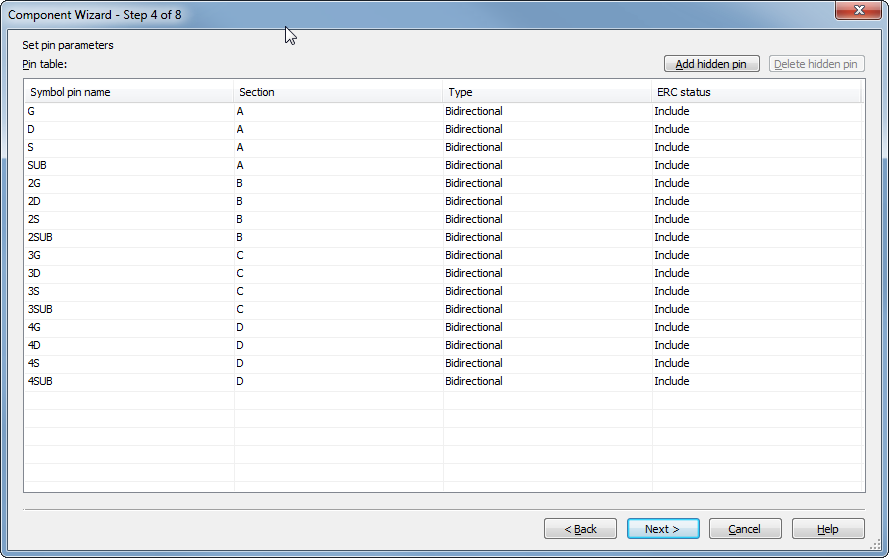

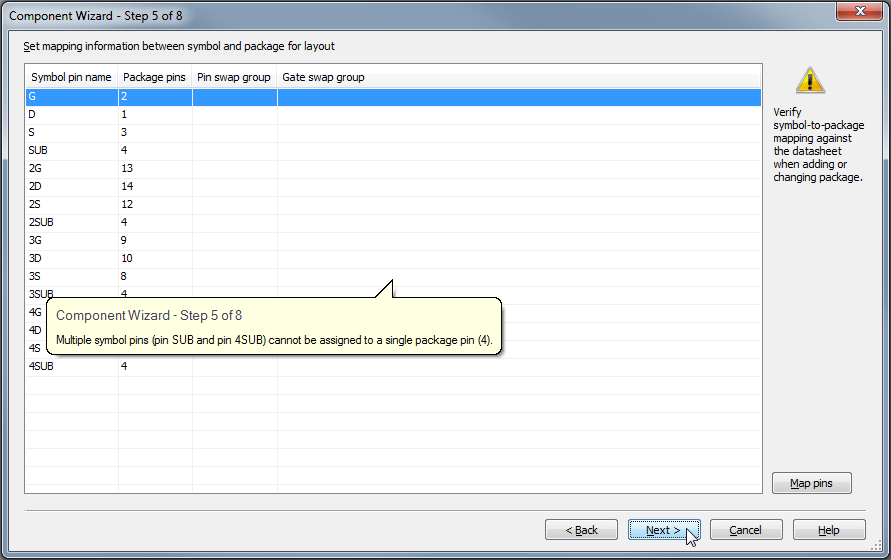

I've attached a doc with my steps.

P.S.. Sorry for the late response.

Thanks

Moses

07-19-2011 08:59 AM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

Hi Moses,

The last time I looked at the 1106 and 1107 model, I didn't see that they are calling another model called ncg and pcg respectively. I looked at the .lib file you originally posted and didn't see these models in the library file so this library file is incomplete. Where did you get this file?

National Instruments

07-19-2011 09:30 AM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

My lecturer got it from ALD and mailed me the contant of the ic_mod.lib file.

Thats is the original data from the mail:

* Library of Advanced Linear Devices, Inc. definitions

*

* Copyright 2004 Advanced Linear Devices, Inc.

* Neither this library nor any part may be copied without the express

* written consent of Advanced Linear Devices, Inc.

* PSPICE version

* $Revision: 1.3 $

* $Date: 6 Feb 2004 00:00:00 $

* ------------------------------

-----------------------------------------------

*

* This library of models and macromodels is being supplied to users as an aid to

* circuit design. While it reflects reasonably close similarity to the actual device

* in terms of performance, it is not suggested as a replacement for bread-

* boarding. Simulation should be used as a forerunner or a supplement to

* traditional lab testing.

*

* Users should very carefully note the following factors regarding these

* models:

*

* Model performance in general will reflect typical baseline specs for a

* given device, and certain aspects of performance may not be modeled

* fully.

*

* While reasonable care has been taken in their preparation, we cannot be

* responsible for correct application on any and all computer systems.

*

* In all cases, the current data sheet information for a given real device

* is your final design guideline, and is the only actual performance

* guarantee. For further technical information, refer to individual device

* data sheets.

*

* Model users are hereby notified that these models are supplied "as is",

* with no direct or implied responsibility on the part of Advanced Linear

* Devices for their operation within a customer circuit or system. Further,

* ALD reserves the right to change these models without prior notice.

*

* The macromodels listed in this library represent typical performance

* characteristics, without offset (Vos) adjustment, or other

* parameters that would allow for Monte Carlo simulation of these circuits.

*

* Advanced Linear Devices provides a separate library of ASIC standard cell

* functions such as operational amplifiers, timers, and comparators as well

* as resistors, capacitors, and individual transistors and diodes for func-

* tion specific integrated circuit design. This ASIC verification library

* contains a comprehensive set of parametric values to be used in Monte

* Carlo simulation of user designed integrated circuits. Contact your

* Advanced Linear Devices representative for more information.

* -----------------------------------------------------------------------------

*

* Your feedback and suggestions on these (and future) models will be

* appreciated.

*

*

* Advanced Linear Devices, Inc.

* Customer Support Group

* 415 Tasman Drive

* Sunnyvale, California. 94089

* Tel: (408) 747-1155

* Fax: (408) 747-1286

* techsupport@aldinc.com

* -----------------------------------------------------------------------------

*

* IC_MOD.LIB

* ALD ANALOG MODELS FOR IC MOSFETS IN IC_TRAN.LIB

*============================================================================

* Last Updated Date: 2/6/04 BY:RLC

*============================================================================

*

* SPICE MODELS FOR COMPARISON: ADVANCED USERS

*

* These models have been fitted to the ALD device structures.

* For short channel or "digital" transistors, use the digital library transistor models in id_trans.lib.

*

*============================================================================

* N-channel TRANSISTOR models

*============================================================================

* Listing of 1101 transistor models:

*

* --nca 2mv ultra precision matched transistor model. (ALD1101A)

* --ncg general purpose transistor model. (ALD1101)

*

*============================================================================

* Four terminal integrated N-channel ( 2mv. vos dist)

*

.model nca nmos (Level=2

+ gamma=1.09 lot/4/uniform=-.22 dev/uniform=.01

+ vto={.75+vtn} lot/2/uniform=.2 dev/uniform=1e-3

+ Uo=650 lot/3/uniform=40 dev/uniform=.5

+ Ucrit=0.7e4 Uexp=.1 Vmax=1.6e5

+ phi=.70 tpg=+1

+ nsub={1e16*ires} neff={10*ires} nss=.7e11 nfs=1.17e11

+ tox={.055u*cox} lot/8/uniform=9.1% dev/uniform=.05%

+ Cgso={.94n*cox} Cgdo={.59n*cox} Cgbo={.138n*pox} Xqc=.42

+ cj=.39m mj=.5 cjsw=264p mjsw=0.18

+ xj=2.0u

+ ld=1.6u lot/uniform=.19u dev/uniform=.15u

+ wd=1.05u lot/uniform=.41u dev/uniform=.1u

+ pb=.9 js=20.u lot/uniform=50% dev/uniform=80%

+ jssw=2.07e-10 lot/uniform=50% dev/uniform=80%

+ kf=.75e-28 rsh=10 lot/1/uniform=4 dev/uniform=.5)

* 1101 instances use: nrd=.03 nrs=.02 nrg=25 nrb=35 for big devices.

*--------------------------------------------------------

* Package model devices -four terminal integrated N-channel @ vbs=0, grade: a, vos=2.0mv worse case

* mismatch no MC.

*

*--------------------------------------------------------

* Four terminal integrated N-channel (.040 vos dist).

*

.model ncg nmos (level=2

+ gamma=1.09 lot/4/uniform=-.22 dev/uniform=.04

+ vto={.750+vtn} lot/2/uniform=.2 dev/uniform=19e-3

+ Uo=650 lot/3/uniform=40 dev/uniform=5

+ Ucrit=0.7e4 Uexp=.1 Vmax=1.6e5

+ phi=.70 tpg=+1

+ nsub={1e16*ires} neff={10*ires} nss=.7e11 nfs=1.17e11

+ tox={.055u*cox} lot/8/uniform=9.1% dev/uniform=.05%

+ Cgso={.94n*cox} Cgdo={.59n*cox} Cgbo={.138n*pox} Xqc=.42

+ cj=.39m cjsw=264p

+ xj=2.0u

+ ld=1.6u lot/uniform=.19 dev/uniform=.02

+ wd=1.05u lot/uniform=.42 dev/uniform=.1

+ pb=.9 js=20e-6 mj=.5 mjsw=0.18

+ kf=.75e-28 rsh=10 lot/1/uniform=4 dev/uniform=.5)

*--------------------------------------------------------

*============================================================================

* P-channel TRANSISTOR models

*============================================================================

* Listing of 1102 transistor models:

*

* --pca 2mv ultra precision matched transistor model.

* --pcg general purpose transistor model.

*

*============================================================================

* Four terminal integrated P-channel ( 2mv. vos dist)

*

.model pca pmos (level=2

+ vto={-.74+vtp} lot/5/uniform=.2 dev/uniform=1e-3

+ gamma=.58 lot/7/uniform=.2 dev/uniform=.01

+ Uo=260 lot/6/uniform=20 dev/uniform=.6

+ Ucrit=1.0e4 Uexp=.16 Vmax=3.0e5

+ phi=.70 tpg=-1

+ nsub=1e16 Neff=1 nss=1e11 nfs=1.06e11

+ tox={.055u*cox} lot/8/uniform=9.1% dev/uniform=.05%

+ Cgso={.61n*cox} Cgdo={.39n*cox} Cgbo=.138n Xqc=.42

+ cj=.18m cjsw=322p

+ xj=1.2u ld=.96u wd=.5u pb=.9 mj=.57 mjsw=0.33

+ js=20e-6 lot/uniform=50% dev/uniform=80%

+ jssw=2.07e-10 lot/uniform=50% dev/uniform=80%

+ kf=.75e-28 rsh=90 lot/9/uniform=20 dev/uniform=4)

*

*--------------------------------------------------------

* Four terminal integrated P-channel ( 40mv. vos dist)

*

.model pcg pmos (level=2

+ vto={-.74+vtp} lot/5/uniform=.2 dev/uniform=19e-3

+ gamma=.58 lot/7/uniform=.2 dev/uniform=.03

+ Uo=260 lot/6/uniform=20 dev/uniform=.5

+ Ucrit=1.0e4 Uexp=.16 Vmax=3.0e5

+ phi=.70 tpg=-1

+ nsub=1e16 Neff=1 nss=1e11 nfs=1.06e11

+ tox={.055u*cox} lot/8/uniform=10% dev/uniform=.05%

+ Cgso={.31n*cox} Cgdo={.39n*cox} Cgbo=.138n Xqc=.42

+ cj=.18m cjsw=322p

+ xj=1.2u ld=.96u wd=.5u pb=.9 js=20e-6 mj=.57 mjsw=0.33

+ kf=.75e-28 rsh=90 lot/9/uniform=20 dev/uniform=4)

*

*============================================================================

08-20-2011 01:53 PM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

OK

I got the original file from ALD.

The ic_mod file has a line with .ncg...

02-06-2017 12:53 PM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

I'm also trying to add the ALD1106 but am having problems. When I go in to add the multiple sections I try to add 4 pins per section so that on the schematic each section will have the 4 pins for the mosfet configuration. When I do this it tells me that the Symbol Pin names can't be the same, and when I make them different it tells me that I can't connect pins with different names to the same pin. Am I missing something here that you could easily touch on?