- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

Circuit Help!!

09-16-2020 09:30 AM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

Hi,

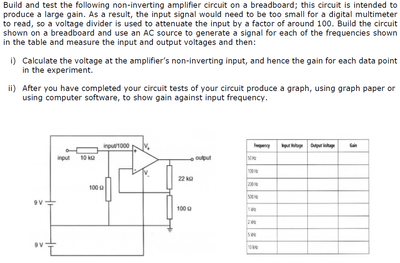

I am trying to replicate the following schematic using Multisim, i believe i have built the circuit correctly but just cant seem to get a change in the input or output voltage when i alter the frequency. Am i taking the measurements from the wrong place or is there something wrong with my circuit? Thanks Guys

09-16-2020 11:45 PM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

Hello,

first, you are referencing your input voltage to the 9V positive supply. It should be referenced to GND. Connect the negative terminal of V3 to GND.

Second, the input voltage divider gives 12V*100/(10k+100)~=120mV amplitude. Then you gain this up by a factor (1+22k/100)=221 which gives 26.5V. However, the opamp supply is only 9V so you will saturate the output at roughly that. The output voltage peak value must be below 9V to actually see the gain you are expecting. You can decrease the input signal amplitude, reduce the divider division ratio or reduce the amplifier gain by an order of magnitude.

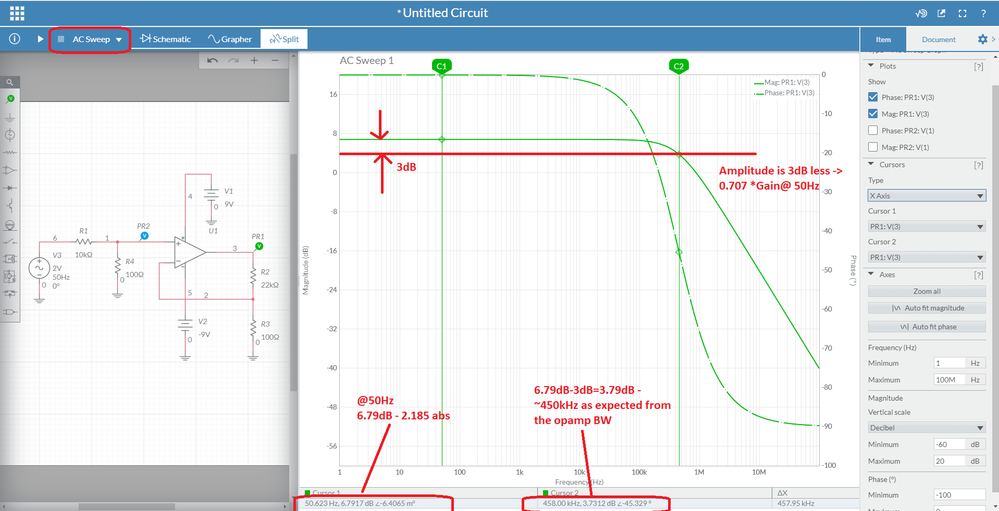

Third, if you click on the opamp and then call the settings (wheel up right) then you will see thet the unity gain BW of the opamp is 100MHz. This means that the actual -3dB BW will be 100MHz/Gain_setting. For example, a gain of 10 will give you 10MHz closed loop BW. This also means that you will only be able to see the BW limitation when setting the input freqency to much higher values (MHz...tens of MHz). Also, remember to decrease simulation time accordingly.

Fourth, if you simply increase the input frequency, the opamp SR (originally set to 1V/us) will transform your sine wave into a triangle. Therefore, you need to also increase the SR setting in correlation with the unity gain BW.

09-17-2020 03:32 AM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

Hi gabor_csipkes,

Thank you so much for taking the time to reply,

You will have to forgive my lack of knowledge of multisim and electronics in general, i am very much a beginner!

I have tried to follow your advice to the best of my ability and have so far done the following:

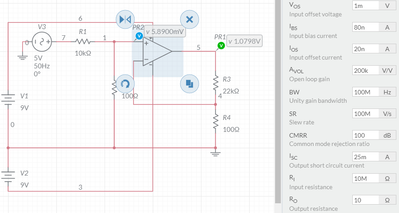

Connected V3 to a ground, i have reduced the input signal amplitude (Volt peak to peak?) to under 5v.

In regards to the opamp unity gain does this need to be changed? i have left this at 100MHz and changed the opamp SR to match, i am unsure of how to decrease the simulation time.

Once i have managed to follow your advice to calculate the gain would this simply be the output voltage/input voltage at that particular input frequency?

I have attached a screenshot of the 'updated' circuit

09-17-2020 04:22 AM - edited 09-17-2020 04:23 AM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

Hi,

let's take it step by step:

1. The negative terminal of V3 to GND is correct now.

2. The 5V is the amplitude. Peak-to-peak it would be 10V.

3. At the divider output you will have now 5V*100/(10k+100)~=50mV. The non-inverting opamp configuration has a gain of 1+R3/R4=1+22k/100=221. Therefore, at DC (or low frequencies) you will end up with 50mV*221~=11V which is still higher than 9V and causes the opamp output to saturate. You can have at the very maximum 9V/221=40.7mV at the opamp + input. Then, considering your divide by 1000 the maximum input amplitude should be <4.07V. You can decrease the V3 amplitude to e.g. 2V or 3V and redo the calculation to see what should happen in DC.

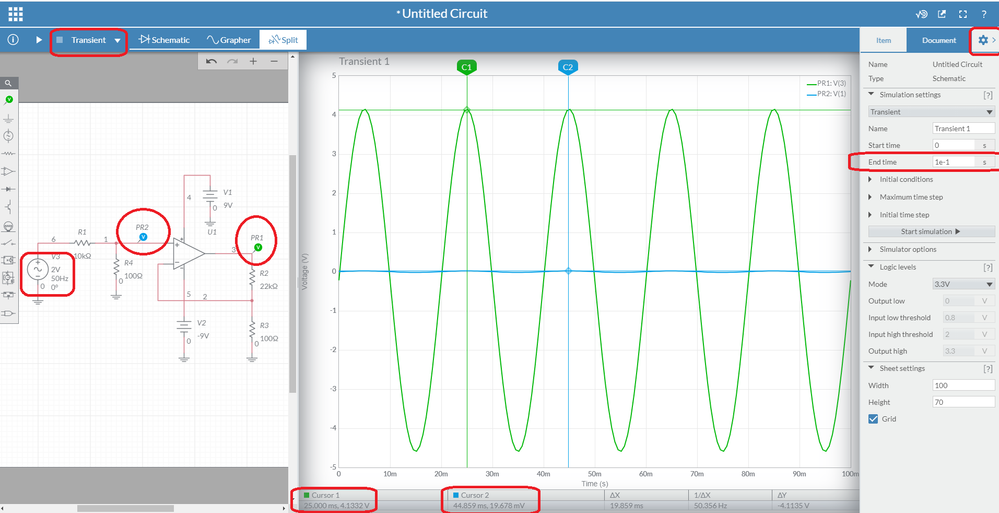

4. If you do your transient simulation with 50Hz input frequency you are within the circuit bandwidth which means that it will behave just like in DC. At 50Hz the input signal period is 20ms. For meaningful results in a transient analysis you need to set the simulation window to see a few periods (5...10?) of the input and output signals. If you choose a transient simulation rather than interactive, you can click on the wheel symbol at the upper right of the window and this gives acces to the simulation "End time" which you should set to 20ms*5=100ms to see 5 signal periods.

5. The unity gain BW of the opamp is set to 100MHz. Therefore, at a gain of 221 you will have a closed loop BW of 100MHz/221=452kHz. To see the effect of changing signal frequency you need to set some frequencies below the 452kHz and some above. Remember that at exactly 452kHz the circuit attenuates your signal with 3dB, that is it will only have a fraction 0.707 of the DC amplitude. The lower you go in frequency, the closer you get to the DC value. The amplitude decreases as you go higher in frequency due to the BW limitation. Whenever you change the frequency remember to adjust the simulation end time such that you simulate 5...10 periods of your signal. In the Grapher settings you can activate cursors and measure the amplitude.

6. The SR limits the maximum slope of the opamp output voltage. The circuit must be capable to drive the entire amplitude (VEE to VCC max) within a fraction of a signal period. 100V/us can be high for many real opamps, but it covers what you need at this stage for your simulation.

7. It might be worth to also perform an AC analysis to see the BW and attenuation guidelines of your circuit.

8. Yes, the gain is simply the output voltage amplitude divided by the input voltage amplitude.

Hope this helps further.

Gabor

09-17-2020 05:14 AM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

Hi Gabor,

Thanks again for your very detailed response, i have followed your steps and with a Vpp of 4v and a input frequency of 50Hz i have achieved the following:

A peak to peak of 983.63mV on the output and 82mV on the input

Does this seem accurate to you, also with the set up i have, should the output always be larger then the input? As when i increase the frequency the output becomes lower then the input.

I'm sorry these questions may seem basic to you but I'm trying to get my read round the basics and its alot harder then i thought!

Really appreciate the help

Callum

09-17-2020 08:45 AM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

That output is still not right. 4V input amplitude is the upper limit of the supported range. Set it to 2V before anything.

With the 2V input and 50Hz frequency the amplitudes you should get are as follows:

At the divider output / opamp positive input: V+=Vin*100/(10k+100)=19.8mV - this is just the operation of a basic voltage divider considering that the opamp input bias current is negligable.

At the opamp output: Vout=(1+R3/R4)*V+=(1+22k/100)*19.8mV=4.376V

See in the screensot what it should look like for 50Hz. The input is first attenuated by 100 and then amplified by 221, so the total gain is 2.21 with the errors caused by small opamp currents and finite gain. Whatever voltage you apply to the input, the circuit will generate 2.21 times as much as long as the output stays within (VEE...VCC).

The above is true at DC and low frequencies. As you increase the input frequency above a few hundred kHz, the BW limitation will kick in and the output will get smaller and smaller. At exactly 452kHz (Opamp unity gain BW / Gain =100MHz/221=452kHz) you will get 3dB less gain than @ 50Hz, that is the amplitude will be 0.707*4.376V=3.1V. See the second screenshot for the AC response.