- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

Labview FPGA. Good practice on modular coding.

Solved!12-18-2012 08:47 AM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

Hi

Setup:

In the FPGA top-vi I have controls communicating settings from host to FPGA. I also have a sub-vi to generate an output based on these settings. I placed the last part in a sub-vi since I want to reuse the code for multiple generators.

Now to the question:

If you want a sub-vi to run forever on the FPGA would you place you outer while loop within the sub-vi or in the top-vi surrounding the sub-vi?

To start with I always placed the while loop inside the sub-vi to have a cleaner top-vi. Now I realized that this is probably a bad idea since I can no longer update the settings for the sub-vi since the top-vi settings controls are not placed in a while loop. In the top-vi I could just read the settings controls in another infinite loop and write them to a global varible, which I then could read in the sub-vi, but this would force the different instances of the sub-vi to use the same global variable (and thus the same settings). Is there a workaround to this problem or should I just always design my sub-vi's to be used within an outter loop rather than having the loop in the sub-vi itself?

Solved! Go to Solution.

12-20-2012 05:58 AM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

Hi Mola

Thanks for your post. I have read it through a couple of times, but I'm not reallys sure about your setup.

Could you try to be a bit more specific about the setup, maybe with some screenshots?

Best Regards

Anders Rohde

Applications Engineer

Natioanl Instrumetns Denmark

12-21-2012 09:33 AM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

For very simple applications, putting the while loop in the top-level VI will let you read/write the controls/indicators as needed which can be the least amount of code. However, as your design gets more complex, you really will want to modularize and use a more event-driven approach.

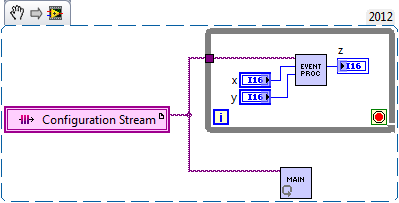

I am going to interpret your application as a main processing loop (i.e. the reusable subVI) with a secondary event loop that monitors for updates from the host and reconfigures the system. If that is the case, I would follow the other pattern you mentioned where I would separate the code into two separate processes (VIs) that run independently. At the top-level, you can construct VI-Defined FIFOs, Memories, or Registers that you then wire to each of those processes to "connect" them together so they can communicate. The host event processing code will be dropped in a loop on the top-level diagram so you can read/write the controls/indicators directly, but hopefully most of the code is inside the event processing sub VI.