- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

1483R for FPGA & 10Tap-8bit question

02-19-2016 12:02 PM - edited 02-19-2016 12:05 PM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

Hi everyone!

My camara is VIEWORKS VC-4MC-M180E0-FM with 10Tap Data Channel

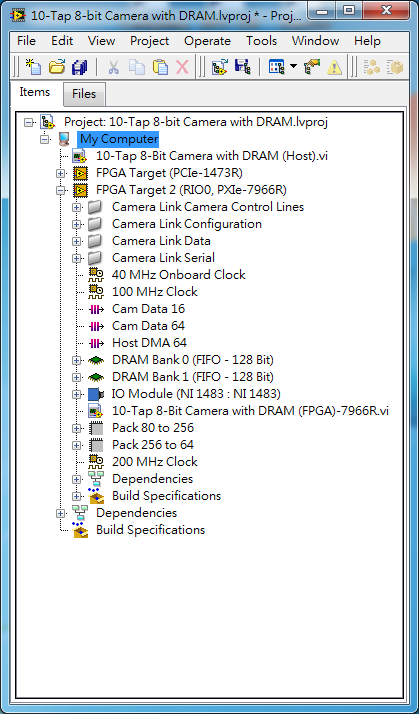

Image Acquisition(IMAQ) is NI 1483R for FPGA Image Processing

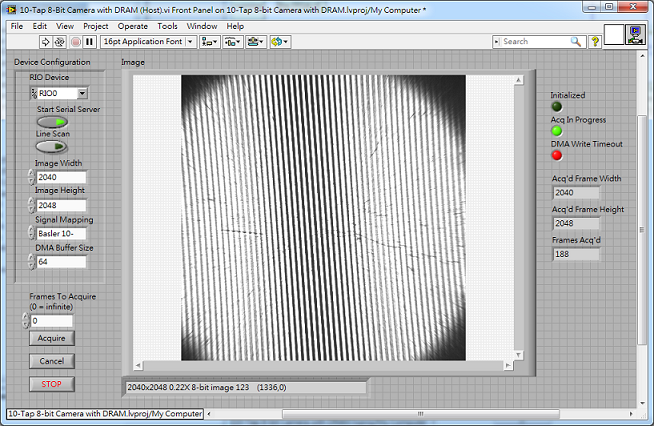

The basic setup of camara is W*H:2048*2040,Signal Mapping:Basler 10Tap,Exposure Time:5000ms

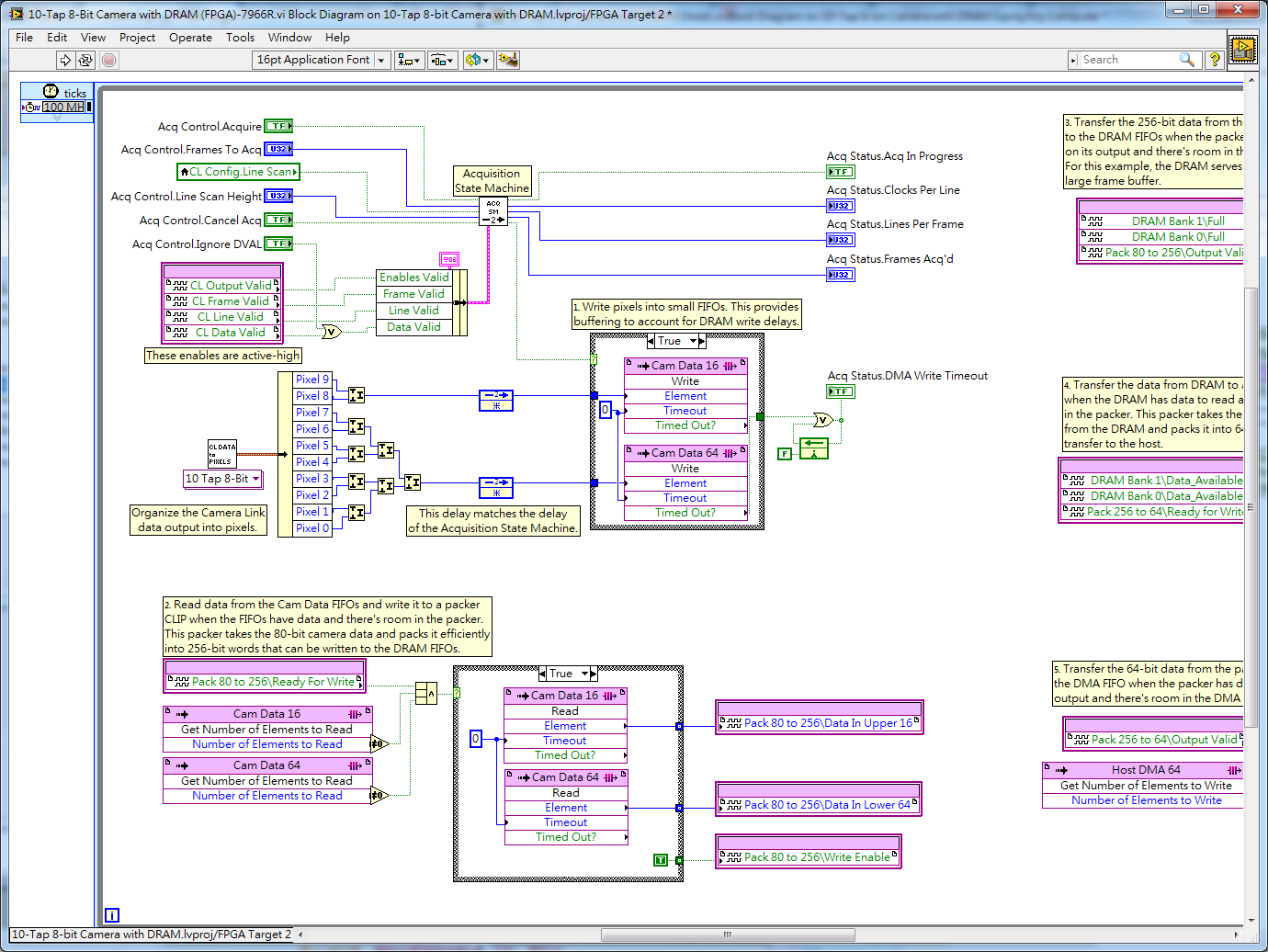

Single cycle Time loop is 100MHz, Four DRAM_FIFO(DRAM Bank 0、DRAM Bank 1、Pack 80 to 256、Pack 256 to 64), Clock Cycle is 100MHz.

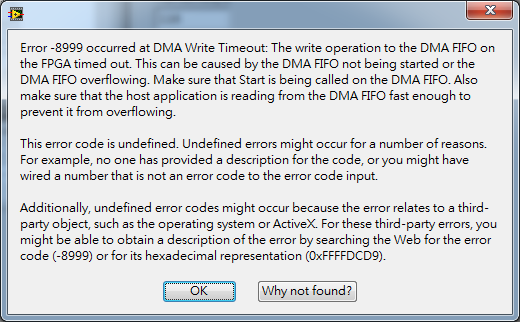

I want to use Labview built-in sample code"10-Tap 8-bit Camera with DRAM" to achieve frame rate of 179 frames/s IMAQ, but when I click "Acquire",the system can only acquire fps of 179frames/1 sec, followed by "DMA Write Timeout" Error Code, as shown in the third picture. May I ask why can't the system acquire frames continously over 1 second? What code or parameters do I need to modify?

Sorry for lacking in experience, want to know if someone can help.![]()

![]()

02-19-2016 01:41 PM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

achieve frame rate of 179 frames/s

and you want that FIFO of camera not to overflow

read faster

02-20-2016 05:50 AM - edited 02-20-2016 05:51 AM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

Hi hatef fouladi![]()

I set Single cycle Time loop is 100MHz

I hope achieve frame rate of 150~179 frames/s.

I try to increase the depth of FIFO(Cam Data 16、Cam Data 32、Host DMA 64), but in vain.

What code or parameters do I need to modify?

02-20-2016 07:31 AM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

I think it could give to appropriate information about FIFO

the link is that

http://forums.ni.com/t5/LabVIEW/Writing-multiple-elements-to-a-FPGA-to-RT-DMA-FIFO/td-p/3253032

02-20-2016 08:23 AM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

So this is likely to be a problem on the host side so if you can share that code it will help.

Some quick numbers to consider though:

180 fps at that size means 752,025,600 pix/sec

Each of these is being formatted into a 64bit sample for the DMA host so this means 8/sample or 94,003,200 samples/second through the FIFO.

So you have to remember for the FIFO, there are two buffers to consider 1) is on the FPGA side and configured as part of the project FIFO element. 2) is on the host side and you configure it through the FPGA interface library, this should be large!

The exact size you need depends on a few factors but a good rule of thumb is it should be at least 100ms worth of data so I would set it to at least 9.4M samples if you can. Obviously this is a big chunk of controller RAM being used but if you can afford to go larger it can never hurt.

If the size looks good, look at your reading code. How many samples does it read? how long does it take to execute or how often does it loop? Make sure that makes sense with the numbers above.

At these rates you also want to make sure you don't start the FPGA too far before you start reading the FIFO else this will overflow before your application even manages to start.

If all of this looks OK then we need to look at the system setup. I see you are using the 7966 FlexRIO. You are starting to approach the maximum rate that this can support so things need to be pretty ideally setup. I'll let you check the other elements first as this starts to get a bit deeper if we need to look at this.

========

Ask me about Rust & NI Hardware

My writings are at https://www.wiresmithtech.com/devs/