- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

pulse patterns with 512us repetition cycle through PCI 7811 with compac RIO

Solved!01-21-2013 10:32 AM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

Can we generate specific pulse pattern of 15 to 30 pulses (500KHz frequency and 0.5us pulse width and patterns are transmitted repetedly with 512us interval) using PCI 7811 with compac RIO. I am having hardware but donot find any help in this regard. If some body send a small vi. for help. I shall be really thankful

Yours sincerely

Solved! Go to Solution.

01-21-2013 05:12 PM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

@Ali211 wrote:

Can we generate specific pulse pattern of 15 to 30 pulses (500KHz frequency and 0.5us pulse width and patterns are transmitted repetedly with 512us interval) using PCI 7811 with compac RIO. I am having hardware but donot find any help in this regard. If some body send a small vi. for help.

Can you please clarify what you mean by 500kHz frequency and 0.5us pulse width? Is this a digital pattern (every 0.5us is a new segment, which could be either high or low) or a series of fixed-width pulses? It would help to draw a diagram showing the desired output.

The 7811 is a RIO device, but not a compactRIO. It has an FPGA. Do you have the FPGA toolkit? If not, you will not be able to program it. If you do, this should be a simple matter of a timed loop with an appropriate wait, and writing to the digital output line.

01-21-2013 10:32 PM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

The 500Khz frequency is for pulses in pattern meaning that there time period is 2us and ON time is 0.5us. Some pulses can be ON and some can be OFF like 110010101110101. The same type of pattern will be recieved after transmission and next pattern with little change is transmitted after 512us interval. The interval is between first pulse of first pattern to first pulse of second time transmitted patterns.

Your sincerely

01-21-2013 11:54 PM - edited 01-22-2013 12:11 AM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

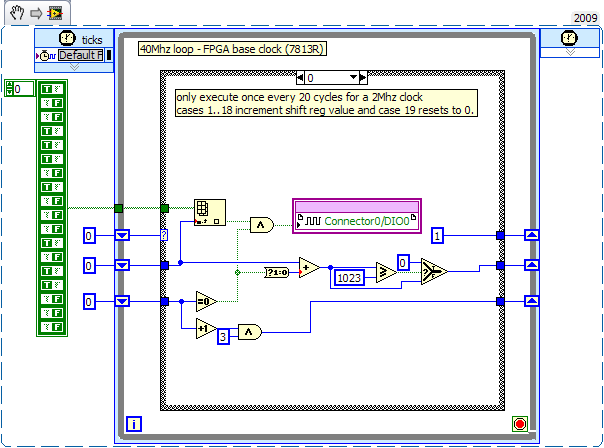

Here's a VI I put together quickly that outputs a fixed pattern. It's barely tested, but it does compile on FPGA. Outputting more than one pattern will require more code, especially since all arrays in FPGA must be fixed-length. If you need to do multiple patterns, and I'm guessing that you do based on your other forum thread, I would look into using a memory block. I am assuming here that the output during the interval between patterns is equivalent to filling that time with false values (no pulse). If that is not the case then you will need to explain what the output should be during that period.

However, if I've correctly understood that the false case is equivalent to no pulses, then it will be easier to use the digital hardware from your other thread instead of FPGA to do this. Just write a pattern that is 512us long - extend your digital pattern with false values to make it the full 512us period.

EDIT: There are a couple of logic errors in this code. It should count to 255, not 1023, and the pattern isn't right on the first iteration. I hope it's enough to get you started, though.

01-22-2013 01:40 AM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

The problem is that just after transmission of one 15 pulse pattern a similar pattern is to be recieved and compared with sent pattern with in 512us And next pattern is to be transmitted and next pattern will be of 30pulses. The thing you asked about the time after transmission is OFF time means no pulse as far as transmission is considered.

Yours sincerely

01-22-2013 11:22 AM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

You asked for a simple VI that can generate a series of pulses, which is what I posted. If you do not know how to proceed from there, you should spend some time learning LabVIEW through the available help, tutorials and examples; take a training class; or, if you do not have time to do the project yourself, hire someone to do it.

01-23-2013 12:12 AM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

Thamks for help!

I have generated pulses but now i have to recieve that same type of pulse pattern after transmission. I cannot find how to recieve and save in some array. Please help me out.

Yours sincerely

01-23-2013 12:55 AM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

Do you only need to determine if the received pattern matches the sent pattern, or do you need to store the received pattern regardless of what it is? Do you need to process the received pattern on the FPGA, or can you pass it back to the host? How will you know when you start receiving the pattern, especially if it begins with a false value?

The easiest thing to do is to constantly read the digital input and write the value to a DMA FIFO that you read on the host, where you can process it more easily. If you need an immediate comparison on the FPGA, you'll need to design a more complex algorithm that can determine when the received pattern starts and matches it against the pattern that was sent.

01-23-2013 01:07 AM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

Pattern will always start with high pulse. Pattern will come just after the transmission. What ever pattern is I need to store and process (compare with already known pattern).If you sent a vi. it will be really easy as you did previously.

Thanks

Yours sincerely

01-23-2013 11:09 AM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

@Ali211 wrote:

If you sent a vi. it will be really easy as you did previously.

Yes, it will be easy for you if I do the work 😉

Make an effort to do it yourself. I, like most users on this forum, am happy to provide simple examples and suggestions on how to improve code, but I won't write your code for you.