- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

characteristic defect

Solved!06-11-2019 09:27 AM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

The BS170 you specified has a spec sheet here - https://www.onsemi.com/pub/Collateral/BS170-D.PDF

>> I want to add a resistor to the drain so I can change the voltage till 10V without burning my transistor.

Putting a large resistor in the drain means you limit the voltage at the device. Its a simple voltage divider. Rds is ~ 2Ohms from the spec sheet, so the voltage divider is Vresistor = 10V*1000/1000+2 = 9.98V across the resistor and Vds = 0.02V. So the current you measure is the same current you would get if you bias your transistor with Vds = 0.02V. Easy to verify!

So you don't want to do that. Spec sheet says the Max Vds = +60V, so you should be fine at +10V. The DMM will since up to 2A, so you are fine running without it.

Yes, the transistor will warm up. Some of mine operate at 400-500C. 🙂

>> Ramp by pattern

Its in the Signal Pallette, but easiest to use Quick Drop (Ctrl + space) then search "ramp".

Craig

06-11-2019 09:56 AM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

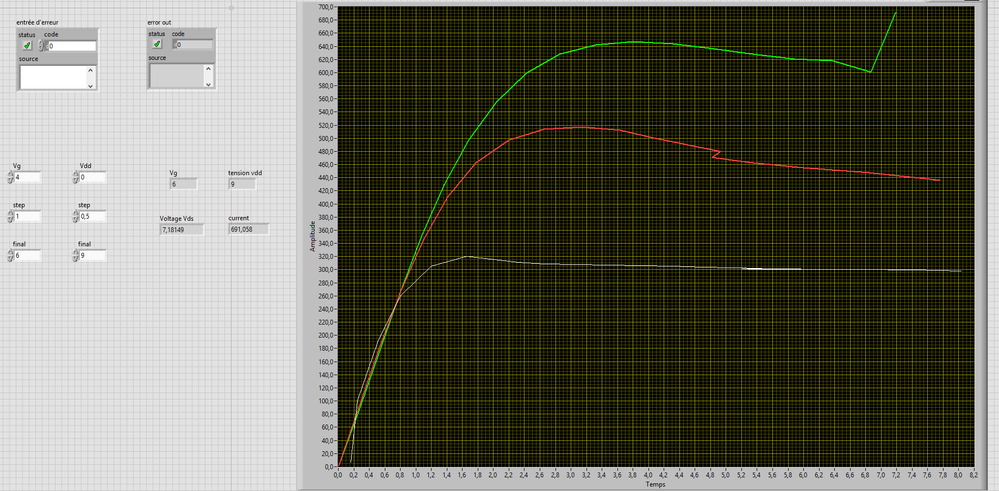

yeah you are right, from the datasheet I should be fine at +10V, but I've just tried without resistor to 9V and my transistor burn out .

In the plot you will see that at VG=6V ,I get to the breakdown region, wich is not expected.

06-11-2019 10:12 AM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

I've just find out that variable power supply Max output:12VDC, 500mA.

DC accuracy for DMM :range 2A= 1350ppm+180ppm .

06-11-2019 10:27 AM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

Typically you do not use a DMM and PSU to characterize a transistor for this sort of testing, ideally you use SMUs which were designed specifically for the purpose. The problem is that the devices aren't stabablized and any spike in Vgs can cause problems - PSUs can be too slow and noisy.

To compensate you should add a bias tee or capacitors in both gate and drain to reduce spurious effects when the PSU changes values. It will change your characteristics to a small degree but make the testing more stable. The other options are to ramp the voltage more slowly, add shielding to the setup, use shielded cables, etc..

Craig

06-12-2019 06:32 AM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

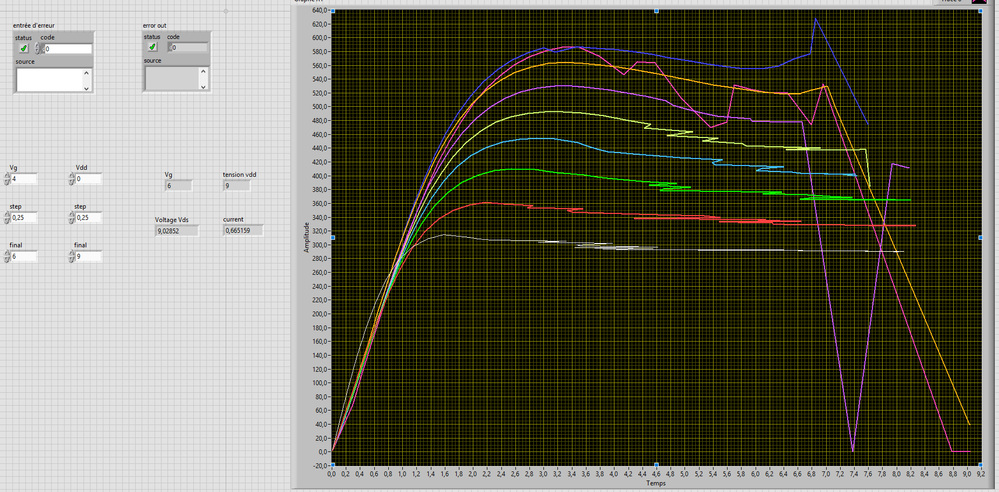

I tried again with a step of 0.25 for each VG and Vds, and my transistor did not burn out with 9V, but from the characteristic my transistor is not stable. I want to add capacitors to the drain and the gate but I don't know how to choise the value of the capacitors.

06-17-2019 10:33 AM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

hi

The problem is that the devices aren't stabablized and any spike in Vgs can cause problems - PSUs can be too slow and noisy.

I am still trying to solve the problem, can I apply a function that block the HF or the parasites before the acquisition of my signal in the VI?

06-17-2019 10:44 AM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

Yes. You should look at how bias tees work - https://en.wikipedia.org/wiki/Bias_tee

Your PSU is the RF and DC source. You want the inductor in line with your device and the capacitor terminated to 50Ohms. Now the values of L and C depending on knowing the characteristics of your source of noise and what you need to filter out. Have a look at the ready made solutions available for a few bucks here..

https://www.minicircuits.com/WebStore/BiasTees.html

But have you tried just using delays before measuring? Coaxial cables and removing the breadboard will also help.

Craig

06-17-2019 12:18 PM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

I checked and I find this, how should i choose the delay, :

slew rate of the output is 20V/us.

timing resolution=50ns.

settling time of the input is for range of 10V :10LSB--1us, 1LSB--2us.(LSB?)

timing resolution=50ns.

I tried with a delay of 1s and a step of voltages 0.25 and i get this :

for the parasites I checked and I find this:

PSU : ripple and noise 25mV.

AI absolute accuracy: noise full scale 280 uVrms.

06-17-2019 12:29 PM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

Coaxial cables and removing the breadboard will also help.

but how I can remove the breadbord because I am using NI Elvis breadbord .

06-17-2019 12:45 PM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

Put your transistor in a shielded metal box. Use BNC feedthroughs, connected to BNC cable to the NI-Elvis board. At the very least add stabilizing circuits to your bread board setup.

I'm not going to do your homework for you, but try 100pf and 50nH. Learn the bias tee theory and adjust as required.

Craig