- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

about using external clock to control the timed sequence

12-23-2013 08:07 PM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

Hi there,

I just find that in LV2013, there supports timed sequence and I can set to use the external clock as the timing source. But I wonder in that case, do I still have to control the priority and CPU resource? In my application, I choose PFI1 as the source of timing and PFI1 is connecting to the an external clock of 5kHz (the frequency of the clock is fix and not changable). But in the labview code, I need 1kHz clock, is there any way to force the clock rate for the timed sequence to 1kHz even though the actual rate is 5Hz?

12-24-2013 10:59 AM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

You can use a Timed While Loop, and two nested Case structures to accomplish the intended behavior.

Plug the Quotient/Remainder vi into the Itteration counter of the while loop, and divide by five. Check for =0? to trigger the outer case.

On the outside of the While loop, keep an array of strings constant, consisting of the individual steps of the sequence. Also add a Shift Register, initialized to Zero. This will be your index into the array, so you will need to increment it each time before you leave the true case.

Use the incremented shift register value and the array size to determine when to quit the while loop.

The innermost Case structure will contain your individual sequence steps.

12-24-2013 04:38 PM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

If you are synchronizing with daq, channel pulses will trigger the loop to execute (assuming it has finished it previous execution). On windows this same thing can be gotten by puting a DAQmx Wait For Next Sample Clock function at the end of the loop.

12-26-2013

05:43 AM

- last edited on

10-16-2024

09:06 AM

by

![]() Content Cleaner

Content Cleaner

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

-Sorry i didn't understand properly, which external Hardware you are using?

-Please add vi, so that it will be more clear.

-Please check this if it helps in anyway for using external Timing source for triggering timed structures.

https://www.ni.com/en/shop/labview/timing-and-synchronization-in-ni-labview.html

uday

12-27-2013 01:55 AM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

@Craig_ wrote:

Timed structures are intended for real time targets and should be avoided on Windows!

If you are synchronizing with daq, channel pulses will trigger the loop to execute (assuming it has finished it previous execution). On windows this same thing can be gotten by puting a DAQmx Wait For Next Sample Clock function at the end of the loop.

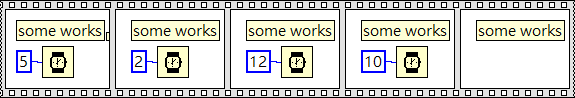

I was using flat sequence and Delay function like below. But it is very bad in time control by using Delay function

Some times it will have extra delay from 3ms to 500ms. That is too much delay. But by using the timed sequence, with setting very high priority, I pretty satisfy with the delay even I used that in windows. As for your suggestion on DAQmx Wait For Next Sample, I don't know how to use that on the sequence (what I am working on is flat sequence not a loop).

12-27-2013 02:00 AM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

@MoviJOHN wrote:

You can use a Timed While Loop, and two nested Case structures to accomplish the intended behavior.

Plug the Quotient/Remainder vi into the Itteration counter of the while loop, and divide by five. Check for =0? to trigger the outer case.

On the outside of the While loop, keep an array of strings constant, consisting of the individual steps of the sequence. Also add a Shift Register, initialized to Zero. This will be your index into the array, so you will need to increment it each time before you leave the true case.

Use the incremented shift register value and the array size to determine when to quit the while loop.

The innermost Case structure will contain your individual sequence steps.

Thanks for your reply. But my question is do we have to divide the clock in code ourselve or just set the clock rate as 1kHz even the actual rate is 5kHz. Using nested loop might cause an issue, I need to control the time in millisecond level, adding nested structure will cause additional time delay.

12-27-2013

02:15 AM

- last edited on

10-16-2024

09:06 AM

by

![]() Content Cleaner

Content Cleaner

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

@udka wrote:

-Sorry i didn't understand properly, which external Hardware you are using?

-Please add vi, so that it will be more clear.

-Please check this if it helps in anyway for using external Timing source for triggering timed structures.

https://www.ni.com/en/shop/labview/timing-and-synchronization-in-ni-labview.html

As shown in above code, I have an external clock signal connected to PFI0 pin which will be used as the counter clock. And I use the counter clock to drive the timed sequence. But my external clock (is a circuit created by 555 timer and output constant rate of 5kHz) is working at a fix frequence, if I set the rate to be 1000, so will the timed sequence use 1kHz or 5kHz as the clock? When I use external clock as source, what is the unit of Start time. always 1ms or something else? Sorry, I don't have the hardware to test the code now so I want to post the question here.

12-30-2013 09:18 AM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

Hi dragondriver,

I have some questions that might help answer this:

- what DAQ hardware are you using?

- what is the bigger picture? Why do you want to do this?

12-30-2013 01:46 PM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

@National_Burritos wrote:

Hi dragondriver,

I have some questions that might help answer this:

- what DAQ hardware are you using?

- what is the bigger picture? Why do you want to do this?

Hi Burritos,

I am using 6711. The reason I need the timed structure as shown in the last diagram is that in each frame, I need to perform some tasks and to output some digital or analog to external device. The timing (millisecond level) is very critical. In my old code, I only use the Wait to control the timing but it is very possible it miss the right time before jump to next frame, which cause unexpected result on the experiment. I then find the time structure, I try that with the builitin timer and highest priority, I found that it helps and the result is much better though it still have delay sometimes. So I am thinking to use external clock to drive the timed structure so the Wait between framew do not rely on the clock in OS.

12-30-2013

04:46 PM

- last edited on

10-16-2024

09:07 AM

by

![]() Content Cleaner

Content Cleaner

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

It's still going to have to wait to get CPU time from the OS, so using that source won't improve the jitter.

You really need a Real-Time system for this application so that you can get bounded jitter and determinism!

Check out this white paper:

What is a Real-Time Operating System (RTOS)?