- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

Why might my myRIO FPGA DAC output a non-constant-frequency sine wave after parallel processing is implemented?

11-08-2020 05:02 PM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

Hello, I am working on designing a PLL, and I found the following version online: https://forums.ni.com/t5/Example-Code/Phase-Locked-Loop-PLL-on-a-myRIO/ta-p/3509103?profile.language...

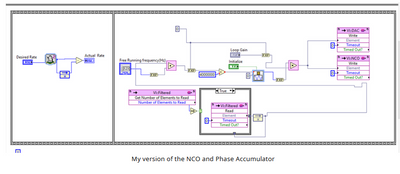

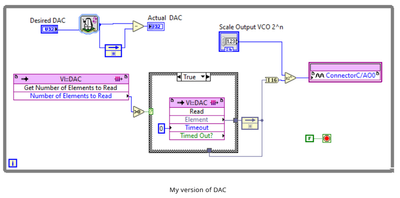

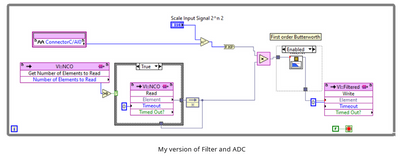

This version showed in the link works well, but I want to increase its speed by implementing parallel processing by dividing the VI into multiple loops. However, after implementing this, my DAC output on the oscilloscope seems to oscillate around the desired frequency even though I have not changed any scaling factors. Does anyone know why this may be? Could it be an issue with my FIFOs?

I also posted this on Reddit, but the LabVIEW forum allows me to include the code, so I am also posting it here as well. I hope that that is ok. If it isn't let me know. The original FPGA VI is called "myRioPLL.vi", and it is under "FPGA Target". The one that I created to implement parallel processing is called "myRioPLL_J3.vi", and it is under "FPGA Target -> Custom".

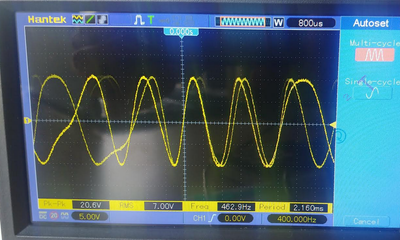

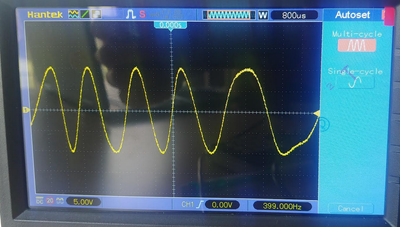

I have attached snippets of my code below along with pictures of my oscilloscope readings. The first oscilloscope reading is of it running normally, while the second is a capture of a single sequence.

- Best regards, 2001J

11-08-2020 08:45 PM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

The Good News is You Did the Right Thing by attaching your Project! Now we can "see" your code, compile your code, execute your code, etc., rather harder to do with (tiny) pictures!

The other Good News is that there are some FPGA Experts on this Forum. I'm a relative beginner with FPGAs (less than a year), so I'm hoping one of them steps forward.

Bob Schor

11-08-2020 10:47 PM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

Hello Mr. Schor,

Oops, I didn't realize how small the pictures were. I apologize for that. While initially posting, I was on my laptop with the screen taking up only half of it, and that may have distorted my idea of their sizes on the post.

And even if you are not an expert at the FPGA, thank you for still replying to my post. It is always nice to receive acknowledgment on a forum.

- Best regards, 2001J

11-08-2020 10:49 PM - edited 11-08-2020 10:50 PM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

As a side note, I cannot find a way to edit my post at the moment, but clicking the attached photos enables the user to view a larger, more understandable version. I'm just posting this in case someone is unaware.

- Best regards, 2001J