- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

Whether a FIFO channel can receive an array?

11-25-2020 02:19 AM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

Hi~

I have a question about whether a DMA FIFO in LABVIEW FPGA module can transmit an array.

I'm using a NI PCIE-7851R which has 3 FIFO channels available. But in my system, scanning galvanometer requires two output FIFO, sCMOS requires one output FIFO channel, and they need to be written to the host through an input FIFO, so I need a total of four FIFO channels. I am considering whether I can input the two signals of scanning galvanometer into the same FIFO as an array, but currently, FIFO elements cannot receive arrays. Is there any solution? Thank you for your attention.

Betty 🙂

11-25-2020 02:26 AM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

Hi Betty,

@Betty97 wrote:

I am considering whether I can input the two signals of scanning galvanometer into the same FIFO as an array, but currently, FIFO elements cannot receive arrays. Is there any solution?

Solution: don't use arrays!

(You may write the two signals one after the other into the same FIFO…)

11-25-2020 08:17 AM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

@GerdW wrote:

Hi Betty,

@Betty97 wrote:

I am considering whether I can input the two signals of scanning galvanometer into the same FIFO as an array, but currently, FIFO elements cannot receive arrays. Is there any solution?Solution: don't use arrays!

(You may write the two signals one after the other into the same FIFO…)

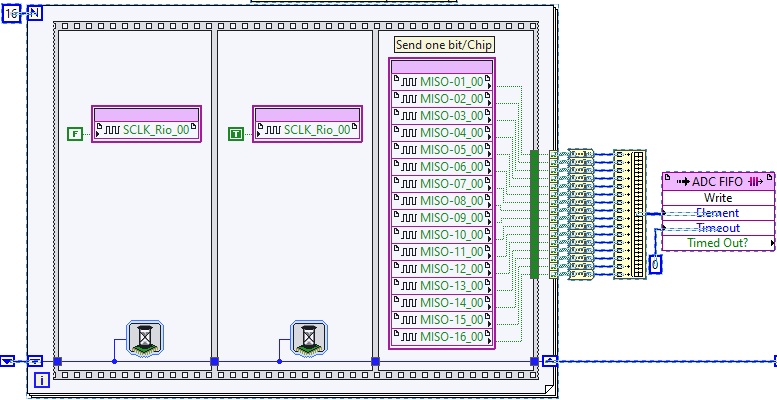

That's very interesting! I'm pretty new to FPGA stuff, but I have 16 A/D chips sending me samples to my RIO, where I've wired 16 of the DIO lines to carry 16 MISO signals from the 16 chips. Not knowing any better, I wired the bits coming out of the 16 MISOs (read in parallel) into 16 "arrays of Booleans", which I convert to U16s (Boolean Array to Number), then Build Array into an Array of U16 which I FIFO to the code running on the Target, which sends the Array to the PC Host. Seems to work just fine ...

Bob Schor

11-25-2020 10:23 AM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

Here is something I've done if I wanted to put together 4 different channels worth of data at the same time in a single FIFO. Let's say it is 16-bit data. I set up a U64 FIFO channel. I use join numbers to combine the 4 into one element to put into the FIFO. On the receiving end, I read the 64-bit integer and use split number to break it up into the individual 16-bit values. (That or typecast it to a U16 array.)

11-27-2020 08:23 AM - edited 11-27-2020 08:27 AM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

@Bob_Schor wrote:

@GerdW wrote:

Hi Betty,

@Betty97 wrote:

I am considering whether I can input the two signals of scanning galvanometer into the same FIFO as an array, but currently, FIFO elements cannot receive arrays. Is there any solution?Solution: don't use arrays!

(You may write the two signals one after the other into the same FIFO…)

That's very interesting! I'm pretty new to FPGA stuff, but I have 16 A/D chips sending me samples to my RIO, where I've wired 16 of the DIO lines to carry 16 MISO signals from the 16 chips. Not knowing any better, I wired the bits coming out of the 16 MISOs (read in parallel) into 16 "arrays of Booleans", which I convert to U16s (Boolean Array to Number), then Build Array into an Array of U16 which I FIFO to the code running on the Target, which sends the Array to the PC Host. Seems to work just fine ...

There is an option in FIFO configuration to state how many elements to enqueue in a single write. I'm not convinced this is what the OP is looking for though. FIFO data have to be single elements of defined data types. You might be able to make a FIFO of a cluster using the "Custom Control" data type. I have not tried this, so no promises.

There are only two ways to tell somebody thanks: Kudos and Marked Solutions

Unofficial Forum Rules and Guidelines

"Not that we are sufficient in ourselves to claim anything as coming from us, but our sufficiency is from God" - 2 Corinthians 3:5

11-27-2020 12:11 PM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

All FIFOs can work with arrays

With DMA-FIFOs you set the datatype and then go to the Interfaces. The maximum number of elements here is based on the FPGA target and datatype. It will be a product of the bits. For example, if the target limit is 64 bits, one U64 or eight U8s. I do not know if this is documented anywhere but I always ascertain the number via the dialog box. The numbers are binary numbers (e.g. 1, 2, 4, 8, etc)

With Target Scoped FIFOs you cannot change the count via interfaces but it does allow for custom controls under the datatype. Make a custom control of a fixed size array and then select that ctl file.

DMA-FIFOs do not allow for custom controls so you would need to bitpack things into an scalar or array.

Certified LabVIEW Architect, Certified Professional Instructor

ALE Consultants

Introduction to LabVIEW FPGA for RF, Radar, and Electronic Warfare Applications