- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

- « Previous

-

- 1

- 2

- Next »

Using VI Scripting to generate FPGA VI

Solved!11-12-2019 10:01 AM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

@Intaris wrote:

wiebe@CARYA wrote:

FPGA Arrays are OK if they're small, but conceptually (sorry if I edited that in after you replied) FPGA memory would work as well.

Ooh, sneaky. 😋

The thing with Arrays is they take not only space for the array itself, but rotating and so on take increasingly more resources the larger the array gets (i.e. the number of elements in the array as well as the size of each element).

But you don't need to rotate the array.

Keep a pointer of the element you set, and increase the pointer. If it's bigger than the array size (preferably n**2, so you can AND the size) start at 0... Getting a delay of 10 is simple by getting (pointer-10) AND size.

11-12-2019 10:08 AM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

Yeah, but then the increasing cost of Array Subset that I linked to earlier comes into play.

So either Rotate is required or dynamic index is required.... Both get expensive fast for arrays.

unless there's another way via arrays?

11-12-2019 10:19 AM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

@Intaris wrote:

Yeah, but then the increasing cost of Array Subset that I linked to earlier comes into play.

So either Rotate is required or dynamic index is required.... Both get expensive fast for arrays.

unless there's another way via arrays?

Why do you need Array Subset? Index Array would do. Or a read from the memory of course.

11-12-2019 10:29 AM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

Zes of course, you're right. Less costly than subset, but still scales badly with array depth.

Same thing applies to Rotate, Subset, Index, Insert, Replace.....

11-12-2019 04:18 PM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

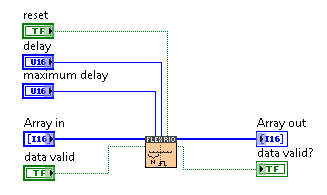

If you're looking for a variable delay buffer the FlexRIO driver installs one. Its used in the default personality FPGA vi for some of our Integrated IO FlexRIO devices, but any FPGA device can use them.

<LabVIEW>\instr.lib\FlexRIO\API\FPGA\v1\Variable Delay.vim

There's also a circular buffer in instr.lib\FlexRIO\API\FPGA\v1\subVIs but it sounds like the variable buffer will get you what you want.

11-29-2019 06:47 AM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

11-29-2019 06:50 AM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

11-29-2019 07:02 AM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

Thank you for your advice.

I actully need to access certain values at each of these delay function, say I need data of i, i(-22), i(-43), i(-335)... all the way down to i (-16383), at the same time, I'm updating the whole serial at 400MHz, so there is really not a easy job to do.

I assume if I set delay to each fixed number instead if using dynamic delay should help me on getting more performance, am I right?

11-29-2019 07:08 AM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

On My! I always thought this delay function is a packed version of "RAM-based Shift Register" in Xilinx IP.

And you point here it doesn't using BRAM or for that?

12-01-2019 09:41 PM - edited 12-01-2019 09:45 PM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

I've not had any issues with IDE responsiveness when using this library.

You won't have access to anything but the oldest element. Its functionally a variable length FIFO. If you need random access you'll need to create a copy of the library and modify it.

When using certain LVFPGA primitives (like feedback nodes) the compiler will sometimes use flip flops, sometimes LUTs, sometimes BRAM. The LVFPGA compiler does a good job of determining what is the optimal resource and instantiates it for you. In this case, if the maximum length of the buffer is of a certain size (I think anything greater than 32 or 64 elements, but don't quote me on that) it will probably use BRAM.

- « Previous

-

- 1

- 2

- Next »