- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

Trouble with High Throughput Math on FPGA

Solved!04-23-2013 01:34 PM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

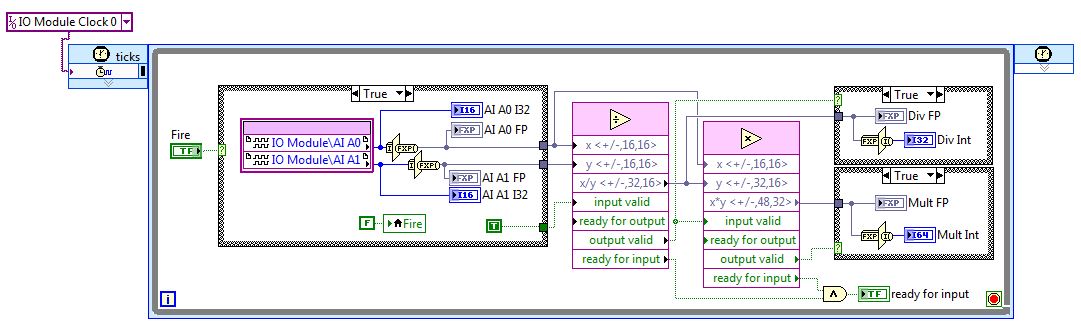

I'm new to Fixed Point numbers and high throughput math on the FPGA. I'm using the 7962 with the 5751 adapter module. I'm writing some simple codes to convince myself I understand what I'm doing before writing the more complex code. I've written a simple code to divide two numbers and then multiply the result with one of the original numbers. The block diagram is shown below.

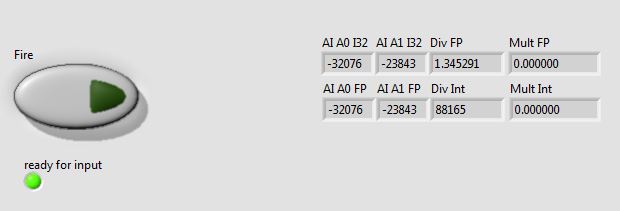

It looks like the divide is working correctly. But the multiply always gives zero and I cannot figure out why. A typical result from the front panel is shown below.

If I remove the divide, the multiply seems to work correctly. Any insight on what I am doing wrong would be greatly appreciated.

Solved! Go to Solution.

04-23-2013 06:22 PM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

After more than a day of scratching my head, I realized that one of the inputs to the multiply function is always zero because it's being read 52 cycles later (i.e. when the case structure is false). To fix this, I added a feed back node, so that the data is carried ahead and is available to the multiply function once the divide function completes. I have attached a picture for those interested/having similar problems.