- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

Tick Count in FPGA Target VI

Solved!03-02-2016 12:53 PM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

Hello to everyone.

I am working on some project, where I use sb RIO 9636. I have to subtract previous and current number of pulses from encoder. Here I attached VI that I use like Target VI. When I use simulated I/O lets say that program works properly. When I compile VI on sbRIO I noticed that LED indicator named x = y? never blinks (although it blinks in simulation). Also, when I put indicaton on Tick Count control, counting starts from some very very big value.

Could anyone help me?

Thanks in advance.

Solved! Go to Solution.

03-02-2016 02:26 PM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

Hi Chupka,

you do some very strange things in this VI…

- you shouldn't use "divide" function(s) in FPGA…

- why are you test tick count for multples of 1000?

- why do you comment "every 1000ms"? There is no wait function in your whole loop!?

- why don't you just have a timer waiting for 1s to trigger your "actual number" calculation?

- you shouldn't use SGL for simple AO generation, especially as your AO expects an FXP value…

- how do you notice a blinking LED when the FPGA runs? Are you able to see a LED going ON for just one 1ms?

03-02-2016 03:10 PM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

Hi Gerd,

thanks for your reply.

- Why shouldn't I use divide functions? It's allowed in Target VI to drag and drop it from Functions Palette...

- I have set Tick Count to count in milliseconds, so I try to take data every 1000 ms = 1s (I have also tried with 10 and 100 ms, results are the same, program doesn't work properly).

- There is no wait function, because wait function only waits specified period of time. My VI doesn't work in background. I have also tried that (perhaps I am not doing it properly). For an example, if I need to collect data every 100ms, how do I set wait function?

- Well, answer to this question is the same as previous answer. Wait function only waits. 😞

- Okay, I will change that. Why not SGL?

- I noticed LED indicator going ON in Simulation. Well, it's not the same as on real system, but still, I thing I could notice some change...

Thanks in advance.

03-03-2016 01:55 AM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

Hi Chupka,

- divide function takes up a lot of FPGA fabric/space

- SGL datatype takes up even more FPGA fabric, so use it with even more care!

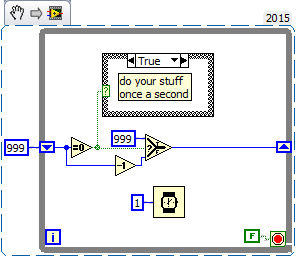

How should your VI work? I guess it like this:

- the loop should run with a certain sample rate (like 1kS/s)

- every second you want to get the latest results (like one result for each 1000 samples)

I would

- put a wait function in the loop to have it run with 1000Hz

- use a counter to countdown from 999 to 0

- when counter reaches zero you output your results and reset the counter to 999…

03-03-2016 03:27 PM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

Hi Gerd,

thank you for your help. I have tried this approach and I have now subtraction of actual and previous number of pulses.

But I have noticed this:

When I change number of thicks in Loop Timer function I get different results of subtraction for the same speed (for an example, in one case 60, in other 210). This function isn't wired with the part of VI that calculates number of ticks. I have implemented counter, as you proposed. I have attached my Target VI below.

Could you explain me what exactly happens and how to choose number of ticks (or ms, or us) for Loop Timer in order to get proper data? I really want to understand it and I can't find brief explanation anywhere.

Thanks in advance.

03-04-2016 01:17 PM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

Hi Chupka993,

I suspect part of the behavior you described is that when you change the Loop Timer, you are changing the speed at which the loop operates. As GerdW stated, setting that Loop Timer gives your code a rate at which it should run. For example, setting that to 1ms means that your code inside that loop will run once per millisecond or 1000 Hz. Ticks would work the same way, but I believe the time scale would be ticks of the FPGA clock which is typically 40MHz on our devices.

When you have the Loop Timer set to 1 millisecond, the code in the loop will execute 1000 times a second, and your iteration counter would be 1000 times before updating the outputs meaning your code runs a full 1000 iterations once a second. If you change the Loop Timer to 2 milliseconds, the loop will execute 500 times a second meaning your 1000 iterations would take 2 seconds to run. I think the behavior you are seeing is because the iterations are occurring faster than you intend.

You should figure out exactly how much time it should take your loop to run 1000 times, and then set the Loop Timer to the proper value to achieve that.

National Instruments

03-05-2016 03:27 AM - edited 03-05-2016 03:35 AM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

03-05-2016 07:37 AM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

Gerd and Gator,

Thanks a lot 🙂 Now I am able to finish my project.