- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

Simulation Interface Toolbox: Problems using sbRIO with Tutorial: "Using the Example Sinewave Model with a VxWorks CompactRIO Target"

09-20-2011 03:58 AM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

Hello

I faced a problem when I tried to do the Tutorial "Using the Example Sinewave Model with a VxWorks CompactRIO Target".

My specifications are:

Software:

Win7 64-bit

Matlab 2010b with RTW (to compile the *.dll) (32-bit)

GNU-Toolchain 6.3 running in Virtual PC-XP-Mode (to generate the *.out)

Labview 2011 with Simulation Interface Toolbox 2011 (32-bit)

Hardware:

sbRIO-9631 (from Labview Embedded Platform Evaluation Kit)

I was able to compile a dll and an out file.

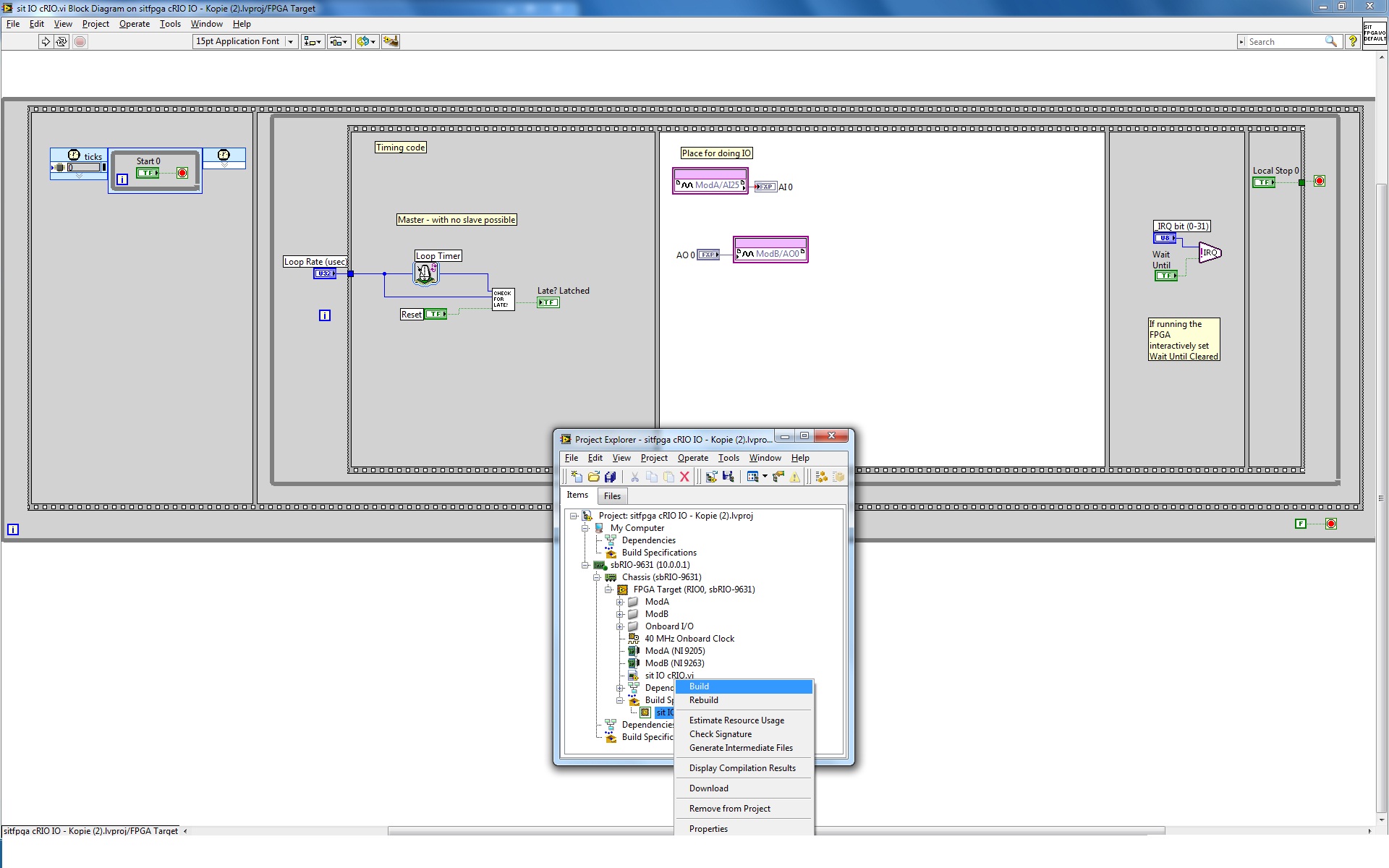

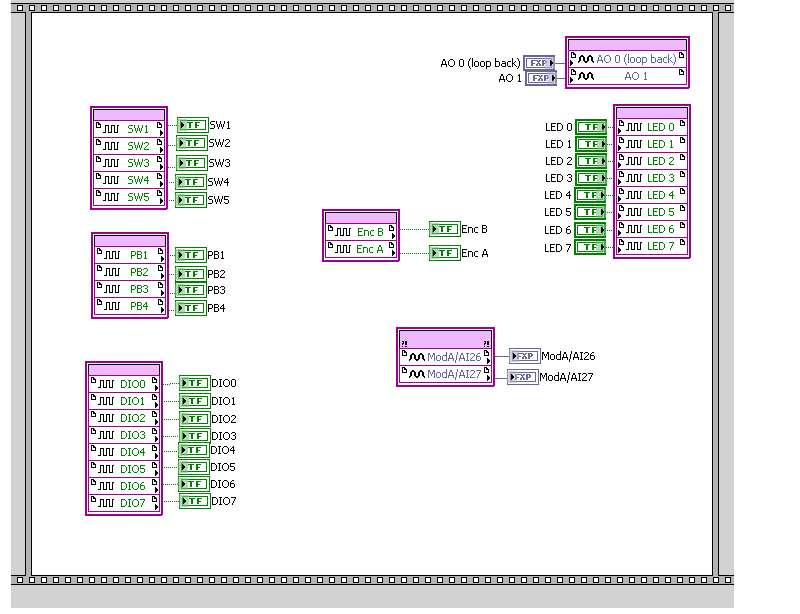

I created a custom fpga-Bitfile with the Tutorial "Creating a Custom FPGA Bitfile".

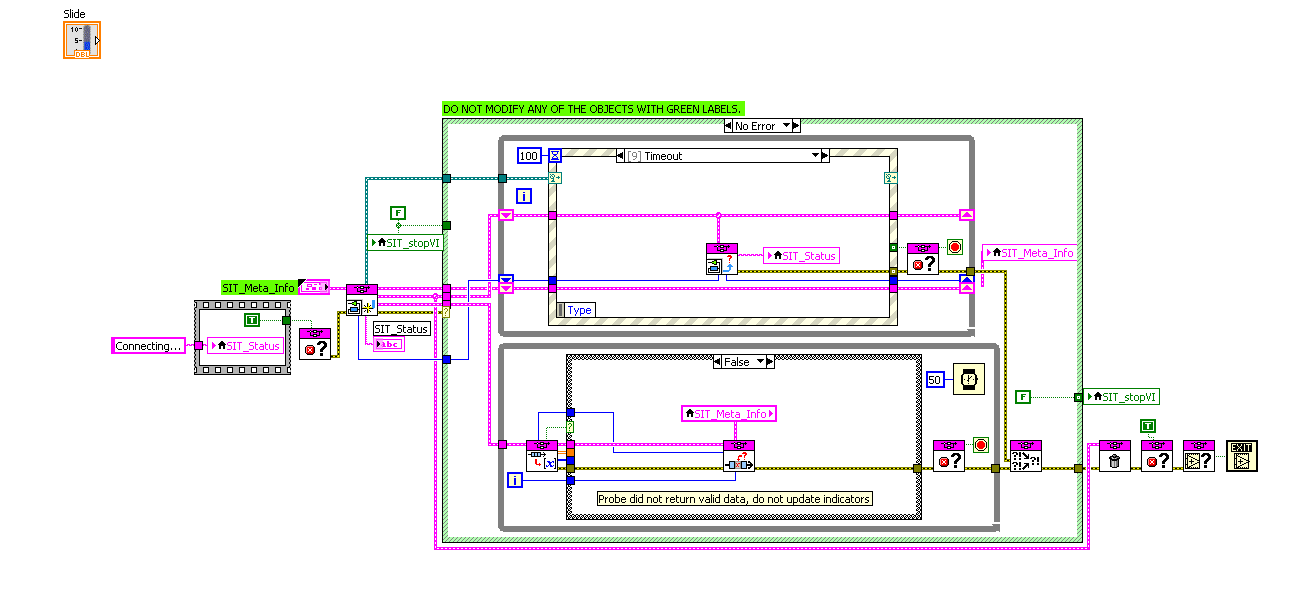

In a blank VI I made the Host-VI and with the SIT Connection Manager I created the Driver VIs.

Until here everything worked fine.

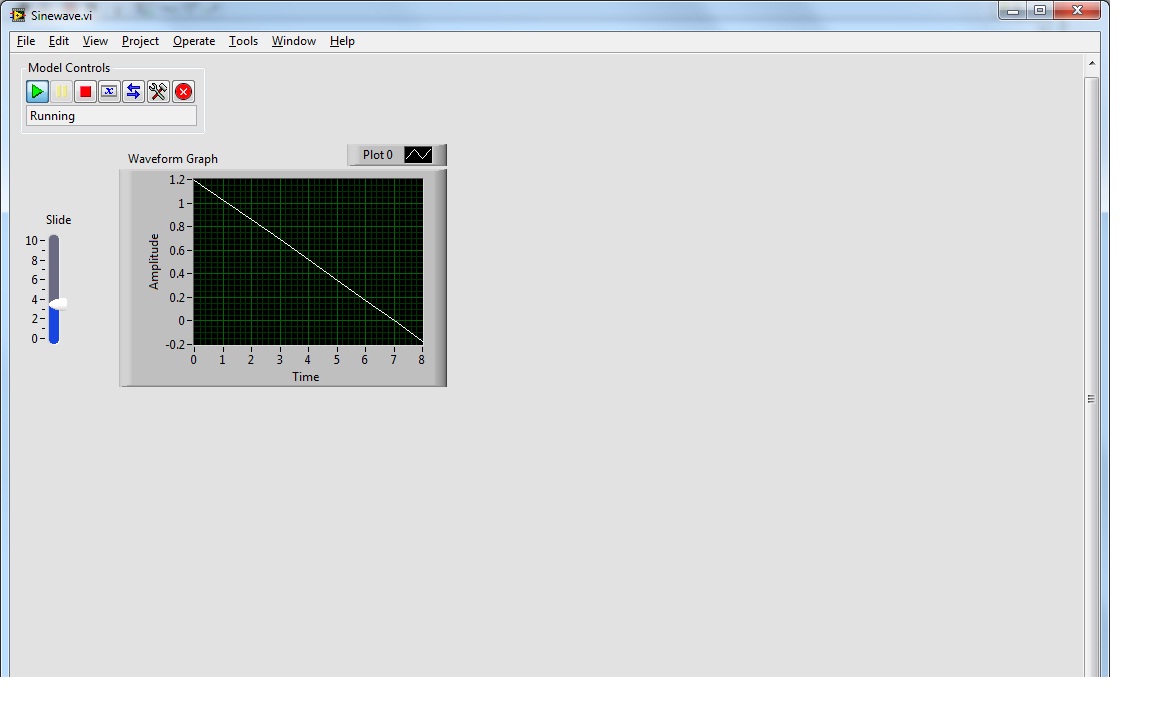

Now my problem appeared. As long as I don't create Hardware I/O Mappings my model runs fine on the sbRIO:

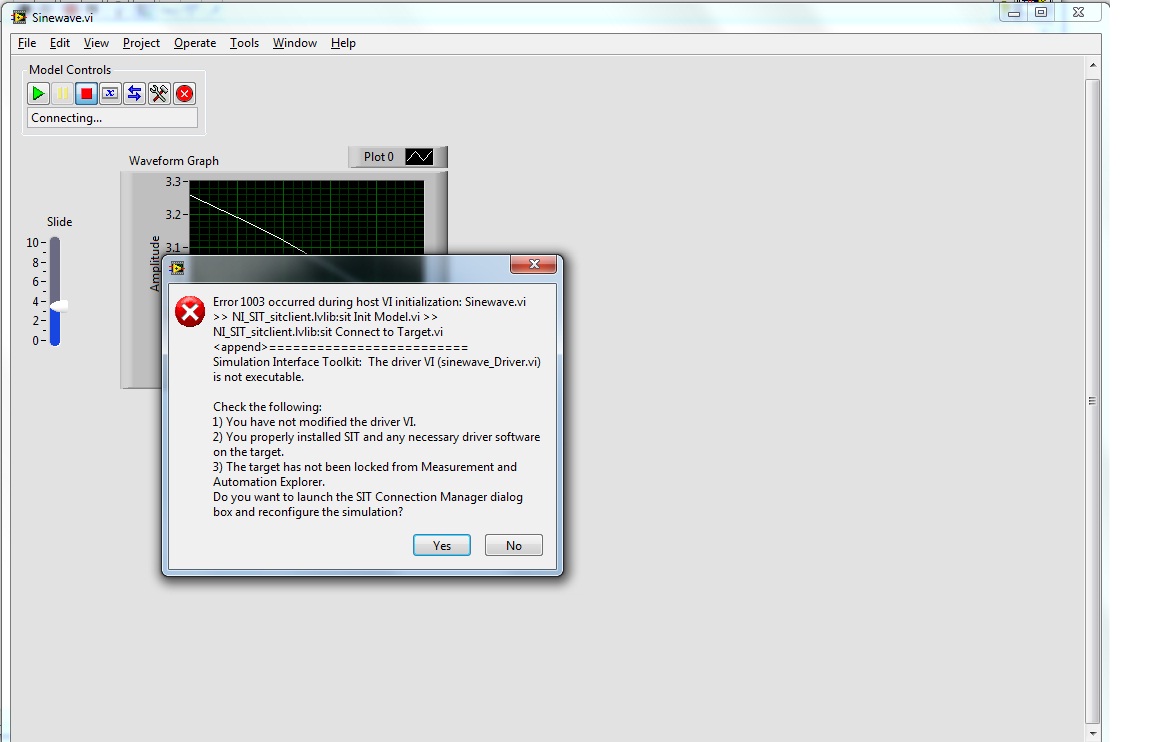

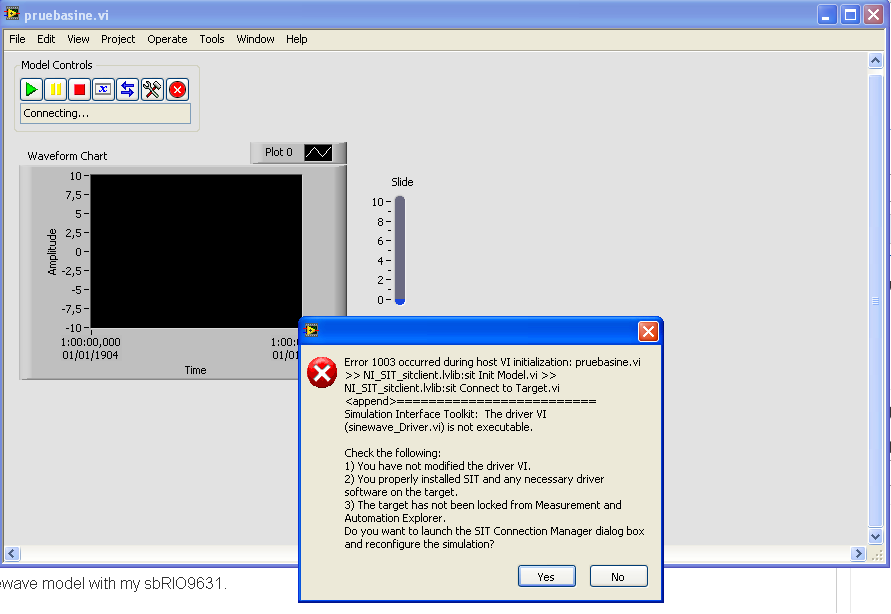

But when I try to map the in and out port of the model to a HW I/O I get this error:

What causes this error?

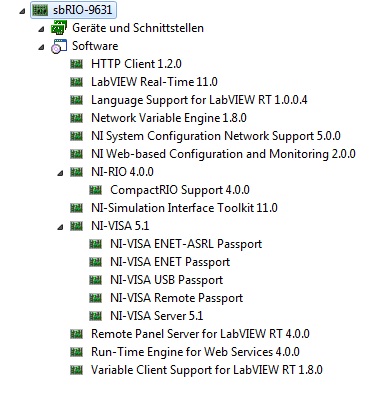

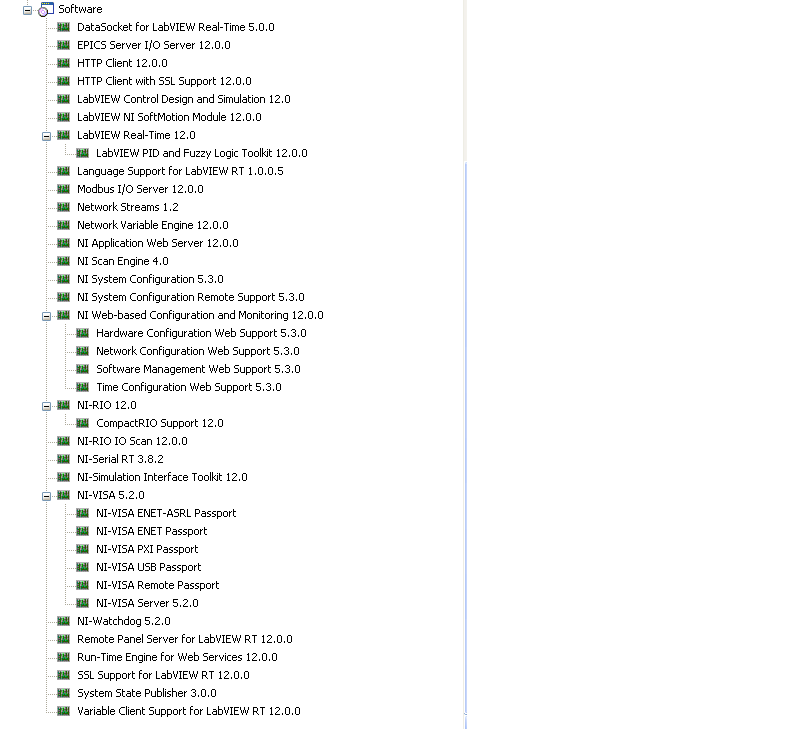

On my sbRIO following software is installed (followed this instruction: Configuring a Real-Time Target to Run the LabVIEW SIT Server)

Best regards

Patrick

09-27-2011 03:56 AM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

Hi Patrick,

please post the driver VI so I can see why you can't run it.

Best regards

Suse

Certified LabVIEW Developer (CLD)

04-22-2013 08:57 AM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

I have exctly the same issue. here is my error

my fpga for the bitfile

and my installed software

04-25-2013 07:26 AM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

Hi,

did you try a repair of the NI-SIT?

Is there any lock in MAX?

Did you modify driver VIs?

Best regards

Suse

Certified LabVIEW Developer (CLD)

04-26-2013 08:46 AM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

Yes. In fact that was the first thing i did