- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

Read/Write lag between the FPGA and RT processor

07-15-2013 02:16 PM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

To be honest, I'm not even sure that's the problem.

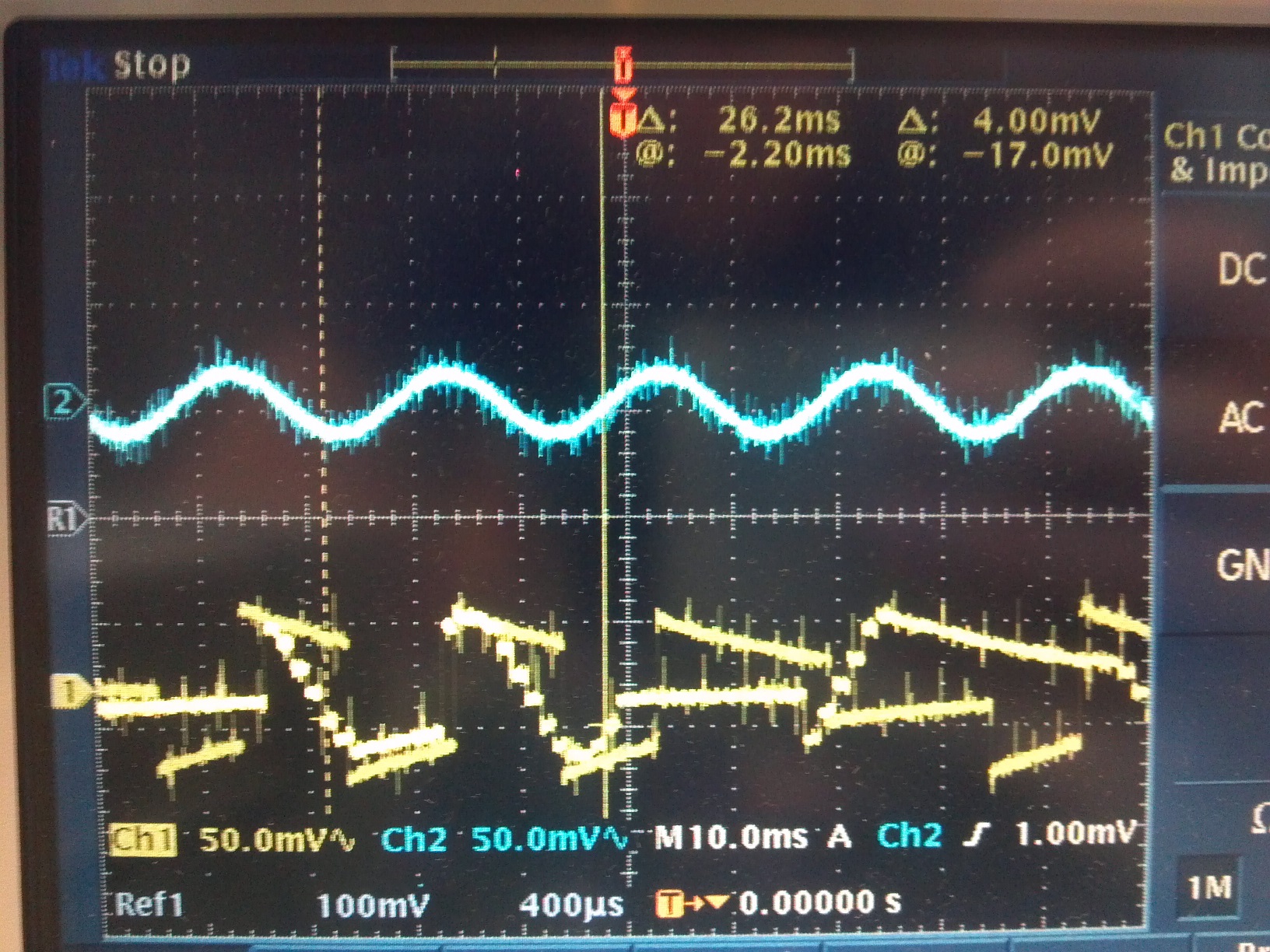

I have a sbRIO-9636 FPGA system which is reading in voltages from a 6-accelerometer array. This picture is basically the problem I am having.

The turquoise waveform is the sum of the accelerometer readings straight out of the FPGA VI (I have it sitting on a speaker putting out a ~50Hz wave). The broken yellow waveform should be identical. I think the picture I took has 2 sequences overlayed, but you can see that for little spurts (ignoring interpolation), it is correct. The VI running on the RT processor is simply reading in 6 variables, adding them, and sending the sum to an Analog Out port on the FPGA.

Basically, I believe that the FPGA Read/Write VI is causing terrible lag and I don't know any workarounds or why it would be doing this at all. I can upload screenshots of any VIs people would like to see, but I really described them fully here.

Thanks!

07-15-2013 02:24 PM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

Is the RT system trying to do any other processing? What loop rate do you have on this process?

There are only two ways to tell somebody thanks: Kudos and Marked Solutions

Unofficial Forum Rules and Guidelines

"Not that we are sufficient in ourselves to claim anything as coming from us, but our sufficiency is from God" - 2 Corinthians 3:5

07-15-2013 02:36 PM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

It also controls the LCD screen and creates an array of the readings, but I have the same problem when both of these are disabled. It is slightly better, but still there.

In the RT VI, adding a "Wait until next ms multiple" makes the problem far worse, so I have no loop timer.

I have also been noticing that over the last week or so the RT microprocessor seems to be getting slower and buggier. When I stop the VI, it takes around 15-30 seconds and a popup comes up saying "Waiting for RT target (NI sbRIO blah blah) to respond: Click here to Disconnect." This never used to be the case, but now stopping the VI is irritating. Is there any kind of factory reset that would help with this? Again, I'm clueless about why this is an issue now.

07-16-2013

11:26 AM

- last edited on

04-28-2025

06:33 PM

by

![]() Content Cleaner

Content Cleaner

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

Hi sra2,

When programming for a real-time environment, you need to consider the fact that the processor will execute tasks according to priority. If you have a loop running at full speed (ie: no waits), the processor will devote all of its additional resources to this loop, which means it doesn't have time to execute any other tasks. It is very important to allow time for all of your desired tasks to complete, and this is done by adding waits, or using timed loops that are longer than the interal code execution time. When the CPU usage is maxxed out, one of the first things to suffer is network communication, which would explain why there are lags when trying to communicate with a host PC. This could be a part of the problem. Try to use timed loops, and make sure to set their priorities according to which tasks you need to finish. Also be sure to leave enough processor time for everything to complete. You should be able to monitor the CPU usage in the Distributed System Manager.

Also, how are you transferring data between the FPGA and RT VIs? Here is some information about the different ways to transfer data, and the pros and cons of each: Transferring Data Between the FPGA and Host (FPGA Module).

You might look into using a buffered transfer method to make sure you aren't losing data.

12-03-2016 02:37 AM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

sra2 I am facing the same issues, did you figure out what caused you latency between the RT and FPGA?

I have spent quite sometime troubleshooting this, I would really appreciate your input.

Cheers