- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

R Series FPGA IO Module in Simulation

10-25-2017 05:52 AM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

Hello everybody,

Since my last post seems to have disappeared from this forum, I'll try again here.

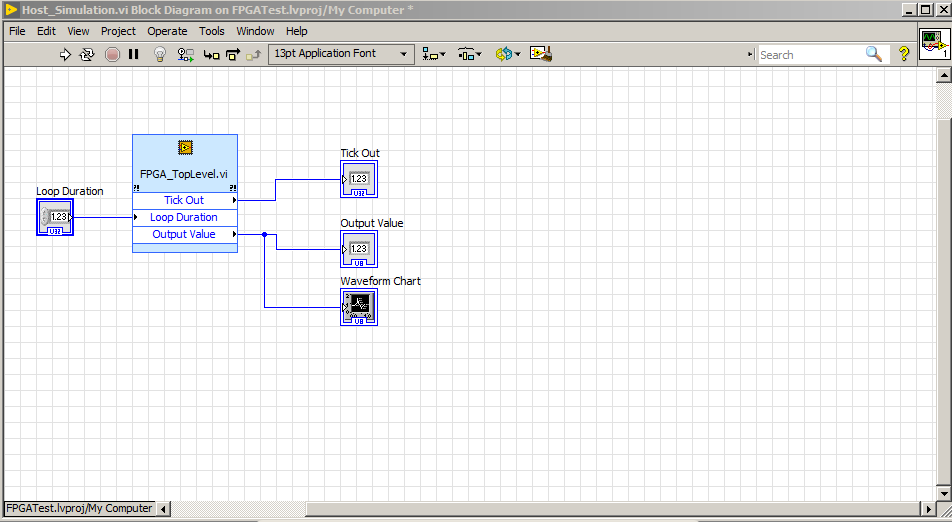

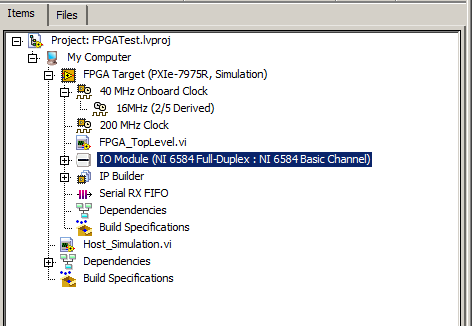

I'm trying to simulate an FPGA VI that targets a PXIe-7975R board with an NI 6584 IO Module. Simulating the FPGA VI itself works okay, however I also want to inspect I/O together with simulated host data.

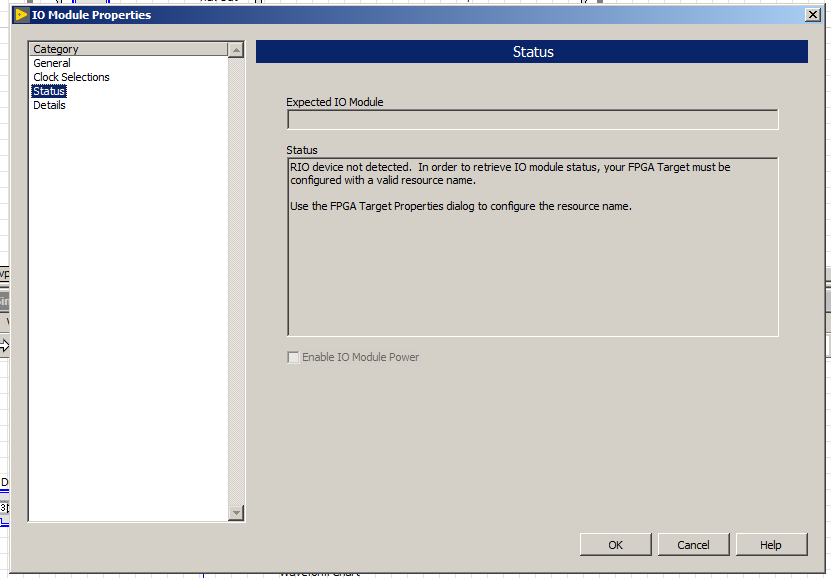

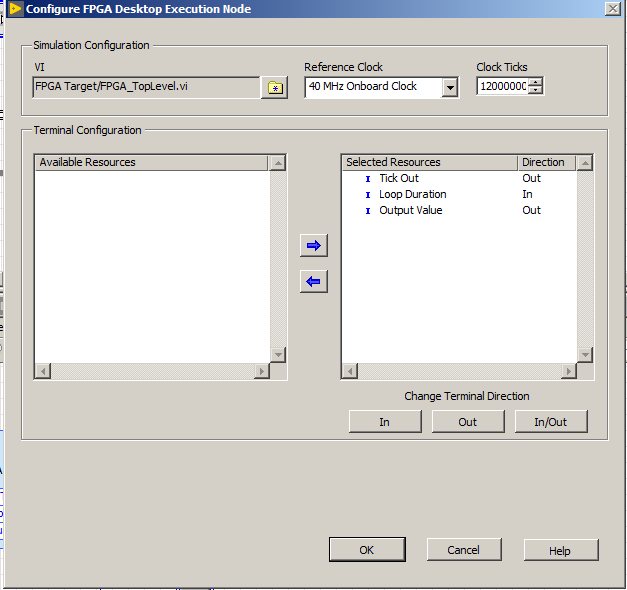

To accomplish this, I created a host VI with an FPGA Desktop Execution Node, selected my Top Level FPGA VI - but the IO Module Ports and Pins are not listed under "Available Resources". The IO Module status (IO Module Properties -> Status) rightfully says "RIO device not detected." as I run this simulation on a regular PC - but that should not affect Simulation of those I/Os, right? I *can* see Basic FPGA I/Os, if I add them via "FPGA Target -> New -> New FPGA I/O", which then appear in the Execution Node Configuration Dialog. However, I can not add IO Module I/Os there.

To provide a minimum working example, I'll be showing what works and what does not. You can find attached pictures of a simple project configuration, FPGA and Host VIs as well as the FPGA Execution Node Configuration Dialog (where I would be expecting the IO Module Pins as I see them in the Project Explorer).

I'm not sure what I am missing, so maybe somebody can tell me...

10-27-2017 09:37 AM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

I always had problems with the desktop execution node, similar to what you are having. I couldn't make it work at all, which was disappointing because on paper it seems like a pretty neat tool.

Instead I just build facsimiles of the code on my desktop and then port it over to the FPGA. This works, but is not ideal as I can make mistakes in the porting.

Hopefully someone will have some more specific advice around how to get the desktop execution mode working.

10-30-2017 03:11 AM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

Well, I checked back with NI technical support and it turns out that I/O module simulation is simply not supported at all. Simulation of basic I/O is working as it should, but I/O modules are simply not to turn up in the available resources. This is a pity.

A possible workaround involves placing front end indicators and controls in the FPGA top level entity, which can then be routed out of the desktop execution node. I place those in a conditional disable structure, to at least keep them from being compiled into the synthesized FPGA design.

However, this is not a problem of the desktop execution node per se, which works really okay for all other purposes. It is admittedly relatively slow for simulation, so simulating loop delays in the millisecond range with a MHz-range clock is probably not the best idea. At least FIFOs and DMA to a host VI (which runs in parallel to the desktop execution node test bench) are supported, which makes it usable.