- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

- « Previous

-

- 1

- 2

- Next »

Questions about FPGA Derived Clock

Solved!02-14-2024 10:24 AM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

Sorry for responding to a nearly 3 year old post, but I stumbled onto this thread and it pains me that nobody ever pointed this out:

Between the requirement you describe here:

Requirement being having a clock period of 13ns or 75Mhz. Which is why I first asked if that is even possible.I mentioned 76.9...Mhz value as an example since it gives a clock period of 13ns.

...and the system clock tolerance range you mention here:

Also also, do you have to hit 76 MHz *exactly*? Usually SPI devices have a tolerance range they can operate in, maybe you can make 80 MHz work?

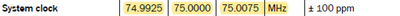

I cannot say for sure but their tolerance range is a bit tight:

I believe you actually want a 75MHz clock, which should be a much nicer clock value to derive (40MHz*15/8=75MHz). My guess is that the 13ns is likely just a description of the 75MHz clock's reciprocal to give you an estimate of the clock's period (1/75MHz=13.3333...ns, which rounds to the nearest integer value of 13ns). Why the 13ns is listed first (or even at all) as a requirement, I cannot say, but I believe it has misled you quite a bit.

06-05-2024 10:12 AM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

It has indeed mislead me. So did some of the information discussed here on this thread. I worked on several projects are this one. After going all crazy, utilizing a 3rd party FPGA, merging that with sbRIO, I learned that you can achieve 75Mhz and 13.3333ns is fine. Also, I have written codes now that operate at 200Mhz on sbRIO's FPGA. IO does work at that speed.

and I appreciate your input. 🙂

- « Previous

-

- 1

- 2

- Next »