- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

Installing and using studica toolkit 4.0.0.4 for myRIO 1900

03-16-2023 08:34 AM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

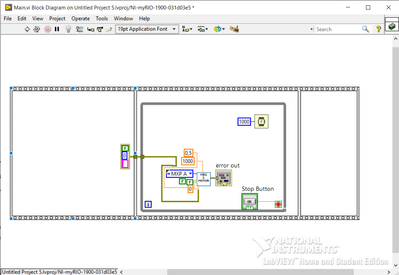

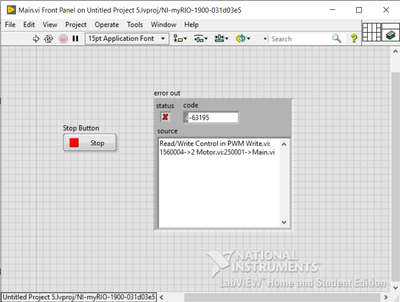

I want to control a motor connected to MD2 board in MXP A of myRIO-1900. I have simple programm below which uses studica toolkit vi to do it.

But when i start program I have this error:

Before programming RIO I read docs how to install studica FPGA personality and updated RIO's FPGA firmware using bitfile below in rar archive. Also I tried to set this bitfile in first frame of my program using "Set custom bitfile" vi in myRIO->Device management, but it still not working.

How can I make it work?

P.S. I know I can write motor controller using fast PWM and DIO vi and use default FPGA, but i need studica toolkit.

03-16-2023 11:14 AM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

The code you sent in my_code.zip (thank you for compressing the Project file and sending the entire Project) looks like the "Welcome to myRIO Accelerometer" Project, and does not resemble the code you showed in your Post.

I don't have any familiarity with the Studica Toolkit 4.0.0.4 for myRIO. But if it is an FPGA Bitfile, similar to one that you would create with the myRIO Toolkit, you should be able to simply load it at run-time when you deploy your code to the myRIO.

Hmm, let me "think out loud" about this -- it might not be quite so simple. I'm opening a LabVIEW 2019 RT Project that uses a custom FPGA that I built as part of the Project, targeting it for the FPGA on the myRIO. The Compiler built for me a BitFile that lives (once compiled) in a folder called "FPGA Bitfiles" inside my Project. The name of the Bitfile has a pattern somewhat similar to the name of your Bitfile, and has the extension .lvbitx, which I think yours does, as well.

The very first thing I do in my RT-Target "Main.vi" is to run a sub-VI I wrote called "Start FPGA". This consists of the following VIs, strung together on the Error Line and connected by the generated FPGA VI Reference:

- Open FPGA VI Reference -- used to identify the myRIO Target and point to the FPGA VI or Bitfile that should be deployed to the FPGA on the myRIO (the Key Step!).

- The FPGA Invoke Method "Reset".

- The FPGA Invoke Method "Run".

- Inside a While Loop, the FPGA Method "Wait on IRQ", with 0 wired to the IRQ Number and TimeOut, with Timed Out wired to "Continue if True".

- The FPGA Invoke Method "Acknowledge IRQ", with the "IRG Number(s)" coming from the "IRQ(s) Assorted" inside the While Loop.

- Set Custom Bitfile, a VI that can be found on the myRIO Palette, Device Management sub-Palette.

So I think I can now "walk you through" the process of getting your Studica Bitfile to load properly. You'll largely follow the steps I described above (I'm not including code, as you are learning to program the myRIO, and the only way to learn programming anything is to write Programs).

Start by creating a Folder in your LabVIEW Project folder called FPGA Bitfiles. Put the Studica Bitfile in there. Now when you move your Project from one PC to another, the Bitfile will move along with your code.

You now need to potentially create the code I described in words, above. I recommend that you write this as a standard LabVIEW Sub-VI. I would name it something like "Start FPGA", and I would give it a Custom Icon (open the Icon Editor, delete the silly-looking generic LabVIEW icon, and at least create a large Filled Rectangle (black border, white or light-colored interior) and in Icon Text write "Start FPGA" (use 2 lines).

Use the default 4-2-2-4 Connector pane, put Error In and Error Out wired to the lower left and right Connectors, and open the Block Diagram

All the VIs go on the Error Line. Put the 6 VIs from the Bullet Points above on the Error Line, and thread the FPGA VI Reference from the output of the (blank) Open FPGA VI Reference through Reset, Run, Wait, Acknowledge, Set Custom, and create an Indicator from the upper Output connector of Set Custom Bitfile. Connect this (on the Front Panel) to the upper Output Connector.

Now for the Magic. Right-click Open FPGA VI Reference, and choose "Configure". Select "Bitfile", and navigate to your Bitfile folder and select the Studica Bitfile, then click OK. You should see the function "fill in" with whatever Icon is associated with the Studica Bitfile. Now locate an Input terminal on this function opposite the FPGA VI Reference output terminal. Right-click it, choose "Create Constant", and a blank I/O Reference will appear. Right-click it and choose an appropriate Input device (on mine, it simply says "RIO0").

That's it. Put this VI as the first thing to run in your myRIO deployed LabVIEW code. It should run and start the custom FPGA code running, returning to you a reference to it.

It is possible that it will "get stuck" in the For loop waiting for the FPGA to send an IRQ. My Custom FPGA code does this, but I don't know about the Studica code. If it runs, and gets "stuck" here, remove the Wait on IRQ and Acknowledge IRQ functions.

One last thing -- you might consider adding a "Stall" vim (look on the Timing Palette) with a 200 msec delay (to give the FPGA a chance to do whatever initializations it needs before starting the rest of your code).

Let us know if this works for you. If not, attach your entire Project again (along with this VI that you just wrote, and the Code that will use the Studica FPGA) and we'll try and help some more.

Bob Schor

04-04-2023 04:13 AM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

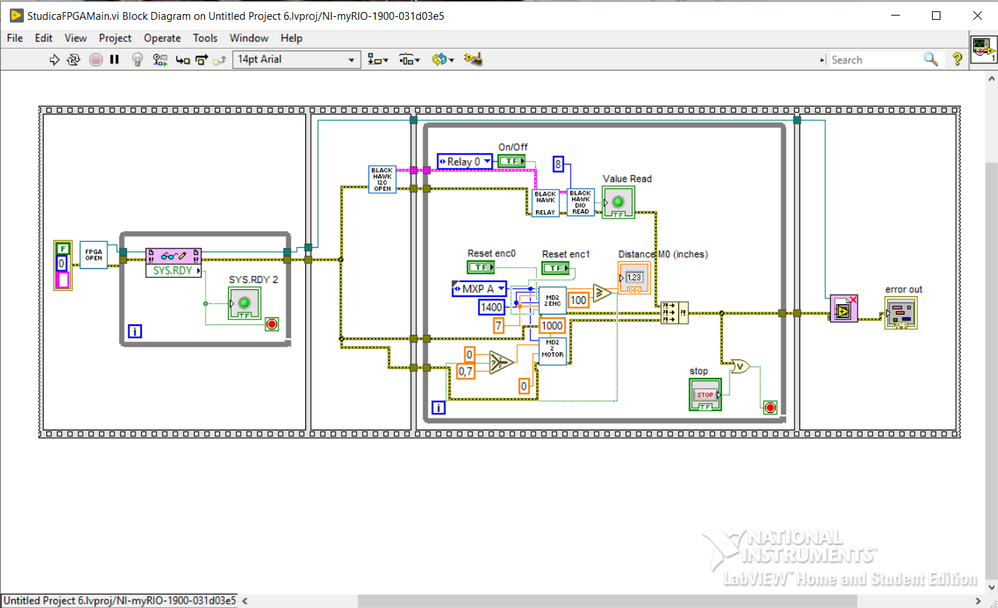

Excuse me for lond delay and attaching wrong project. Thanks for so detailed answer, but I solved this problem at myself.I researched studica toolkit VIs and noticed all of them already have reference to bitfile. I think the problem was in wrong project type: when i tried 1st time I used simple myRIO project that in my opinion forses to use default FPGA personality, so I tried myRIO custom FPGA project and after that it works.

For In my program I use "Open FPGA" vi, that I found in studica toolkit library and wait until system is ready (also I tried without this block and it works as well), next I start my main program and in the end i close FPGA reference