- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

How to understand the serial IO timeout in a cRIO(FPGA interface mode)?

Solved!10-25-2016 10:25 PM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

Hi

I have a cRIO 9075 & NI 9871 to develop a project so I looked for the example of "NI 987x-Serial Loopback" to study first.

However, there are some details I can't figure out clearly.

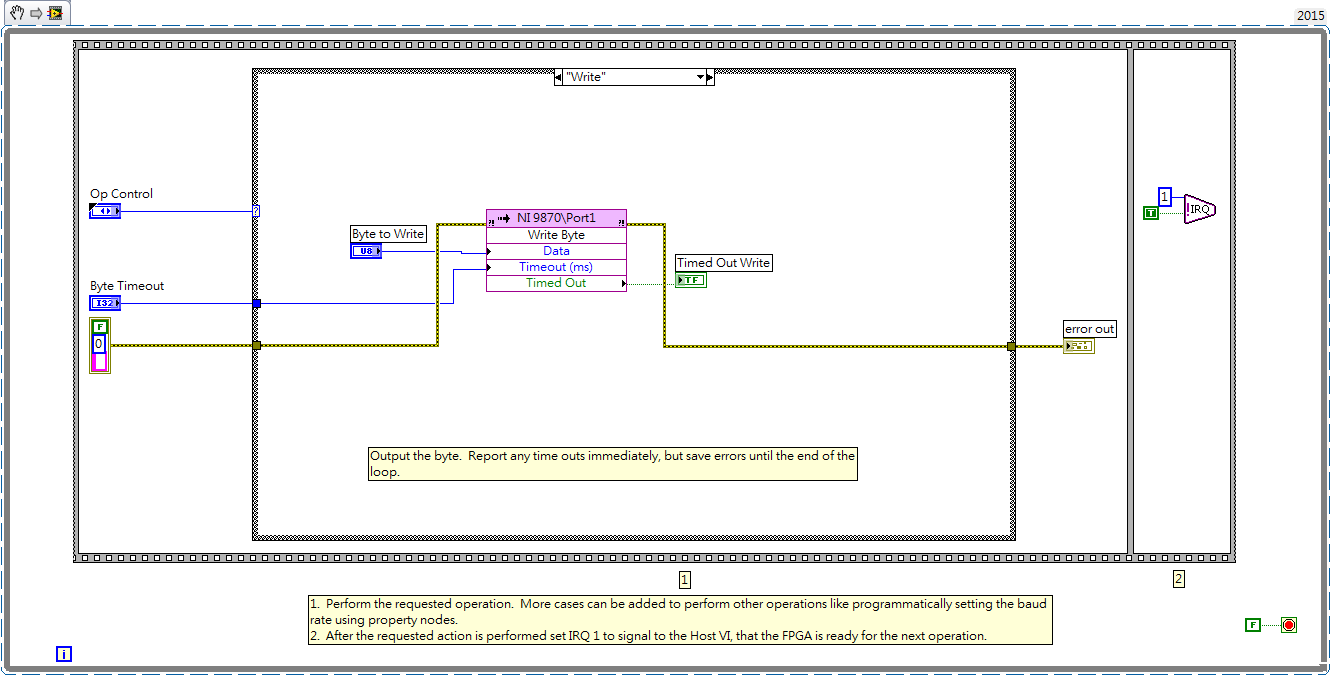

The following image is code from FPGA,

It seems it would update the "Byte to Write" and transmit by FPGA, and then send the interrupt to notify the Host.

The following is the write part of the code from the Host(RT).

It will update the Op Control to write case, and update the "Byte to Write".

My question is what happened if the Write Byte Node in the FPGA code timed out?

In this example, it sets the timeout of the "Write Byte" to 100ms, but if RT is slow, say 1 second, to send the "Byte to Write" to the FPGA, it should be timeout, but I don't know what's the consequence.

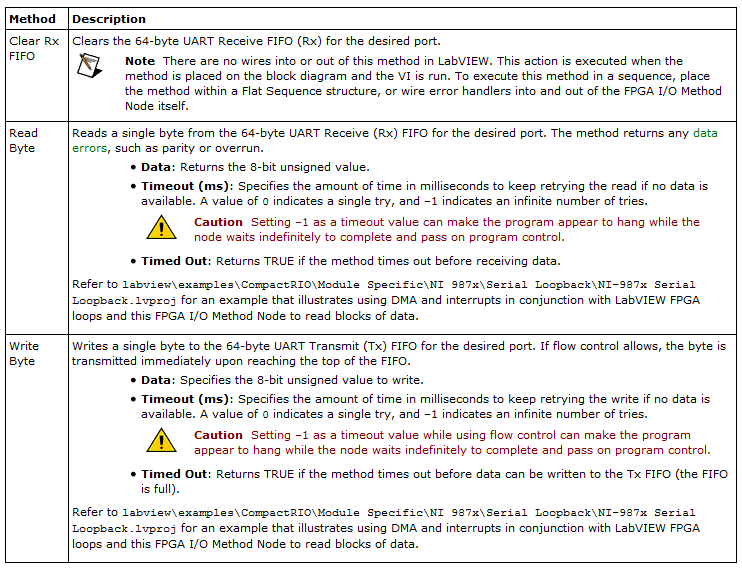

I found out the reference http://zone.ni.com/reference/en-XX/help/370984R-01/lvaddon11/crio-9870/

It mentions that if no data is available, it will keep retrying!!!

As a result, it will retry and retry until the "Byte to Write" being updated in the RT code?

I tried to make my question clear enough, if there's something confused to you in my description, please let me know, I would try my best to explain more.

Solved! Go to Solution.

10-26-2016 04:41 AM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

Hi William,

in case of any RT applications timing is very important. You need to know how much time certain functions take to execute, what functions are not deterministing etc. In this case the timeout for FPGA "Write Byte" was chosen so that we are sure it will not time out during sending the data and at the same time enable the program to function properly (so time out when there is no more data).

I am not sure what is confusing in the documentation you posted. It says: "Timeout (ms): Specifies the amount of time in milliseconds to keep retrying the write if no data is available. A value of 0 indicates a single try, and –1 indicates an infinite number of tries."

If we set it to 100ms, it will retry for 100ms and then time out.