- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

How do i use Timing Loops to Opimize FPGA Code

06-04-2010 06:38 AM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

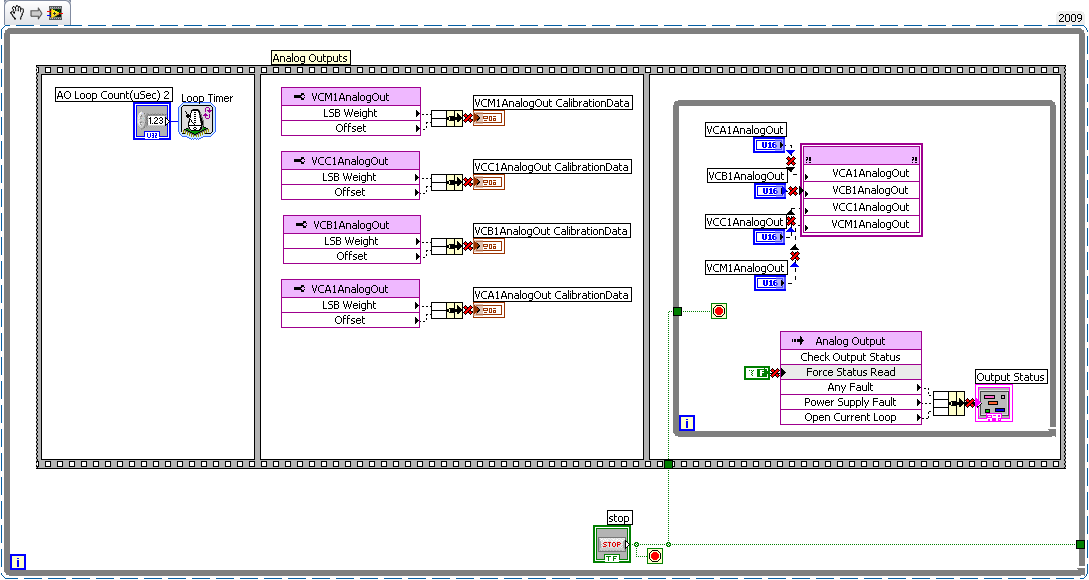

My question is how do i replace the loops with Timing Loops . No cle on how to go about determining the delay, piriority, offset. I've attached a copy of my current FPGA code. I would appreciate it if anyone would be able to help me out in optimizing the code or explain how i should go about doing it

System: Windows Xp, Intel Celeron, Labview 8.0,NIRio PCI-7811R.

06-04-2010 10:29 AM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

Havok,

Can you put the whole project up so that we don't have th broken IO nodes? Thanks, Matt

06-04-2010

12:48 PM

- last edited on

05-26-2025

04:20 PM

by

![]() Content Cleaner

Content Cleaner

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

Look at the help for FPGA. There are lots of tutorials on there that can help you optimize your code:

Using Single-Cycle Timed Loops to Optimize FPGA VIs (FPGA Module)

Pipelining to Optimize FPGA VIs (FPGA Module)

The following KB article should really help:

How Can I Optimize/Reduce FPGA Resource Usage and/or Increase Speed?

06-04-2010 03:55 PM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

On Adnan's note - it looks to me like you are doing a minimal amount (read: no) processing on the FPGA and you are basically just sending and receiving values for IO (so most of the optimization suggestions in the links he provided will not be useful) - are all the FP objects necessary? Is the R-series board even necessary (there is nothing immediately obvious to me in your current VI that suggests it is)? Given that there is no processing going on, I am not sure a SCTL will actually have an impact on the number of slices you are consuming.

Anyway, just a couple of extra thoughts. Cheers, Matt

06-05-2010 06:39 PM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

I got some comments to your code.

First of all you need to think about how the flow of data in LabVIEW is.

Your stop button will not have any impact on you code at all.

None of you while loops will run i parallel, as most of them are just waiting for a input from the stop button.

The stop button has no effect on the inner while loop. There is no way you can stop the loop, as the boolian input is only read once when the loop begin.

If you do get to stop the inner loop, the reset of your while loops will only run once as they will only see a true from the stop button.

And why are you having the outer while loop ?

One thing I have learned is not to have arrays on the front panel, as that will take alot of the slices.

Try to see if you can use DMA's to transfer largeset of data to the FPGA.

06-07-2010 10:06 AM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

06-08-2010 02:00 AM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

I know about the local variable in FPGA, I was just pointing out some of the errors, there are a lot more.

If you take the 3 big while loops, why are they there ? They will only run 2 times. One time until the inner while loop is stopped, and then one short time more, as the stop variable is not read at the same time as the inner while loop.

My suggestion is to drop the 3 big while loops as they have no real purpose. That will allso save some space.

06-08-2010 10:42 AM - edited 06-08-2010 10:42 AM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

06-08-2010 12:35 PM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

I don't know if removing a while loop will reduce the amount of slices used considerably, but it will at least reduce some wiring in the FPGA.

But the removing of while loop was more the the functionality of the code. There are no need for 2 of the while loops as they will only run max 2 times.

But right now I'm missing some feedback from OP.

06-08-2010

02:37 PM

- last edited on

05-26-2025

04:21 PM

by

![]() Content Cleaner

Content Cleaner

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

If you really want to keep the code as is, I would suggest upgrading from LV FPGA 8.0 to LV 2009 SP1. In newer versions of LV you can compile for Size, which optomizes the code to save space, instead of worrying about speed. You can even try it out. (30 Day trial)

There is also a bunch of great resources for optomizing your code as well.

In there you will see information on how reducing front panel objects will greatly reduce your fpga usage. It has to create data space to communicate all of that information back to the host. For example, you have an indicator (AnalogInput1 Calibration) that has an array of 8 cells that has 32 bit numbers in it. Not only does that vi have to compile for every single possible number of that 2^32 bit number, it also has to do that 8 times. You have this same pattern several times and that will definately build up. The better option would be to send all of that data through a dma fifo and read out 9 items at a time, the first 8 items would be the LSB weight, the last item would be the offset (since they are all I32's). You would write them all into one array and put the dma fifo (target to host) in a for loop and then iterate through the for loop writing to host.

Here is more information on using DMA FIFO's in LV 8.0.

Finally, I highly recommend NI's customer education with LV FPGA. Its very useful and I teach it. You will learn these techniques for optomization and many more. Its also available for half-day classes online. Test your FPGA knowledge, if you pass the tests, then don't take the course, if you cannot pass the test, then seriously think about taking atleast the online class.

Regards,

Andrew