- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

HDL node not picking up push button signals

04-20-2013 10:49 AM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

Hello,

I am trying to design a vending machine using sbRIO and Labview HDL node. But my HDL node doesn't seem to pick signals from push button (latched when released). I have successfully done the same thing using labview blocks but not geting desired results by HDL node. I could use labview blocks only and not HDL node but I have to give a presentation to my class about how we can integrate VHDL code in labview. I have attached my VI with following VHDL code living inside HDL node.

process( clk, reset )

begin

if( reset = '1' ) then

state_reg <= idle;

enable_out <= '0';

elsif rising_edge(clk) then

state_reg <= state_next; -- result and enable_out follow input by 1 clock cycle

if( enable_clr = '1' ) then

enable_out <= '0';

elsif( enable_in = '1' ) then

enable_out <= '1';

end if;

end if;

end process;

process(state_reg,Five,Ten)

begin

case state_reg is

when idle=>

if (Five="0"and Ten="0") then

state_next<=idle;

elsif (Five="1" and Ten="0") then

state_next<=statefive;

elsif (Five="0" and Ten="1") then

state_next<=stateten;

elsif (Five="1" and Ten="1") then

state_next<=statedone;

end if;

when statefive=>

if (Five="0" and Ten="0") then

state_next<=statefive;

elsif (Five="0" and Ten="1") then

state_next<=statedone;

elsif (Five="1" and Ten="0") then

state_next<=stateten;

elsif (Five="1" and Ten="1") then

state_next<=statedone;

end if;

when stateten=>

if (Five="0" and Ten="0") then

state_next<=stateten;

elsif (Five="0" and Ten="1") then

state_next<=statedone;

elsif (Five="1" and Ten="0") then

state_next<=statedone;

elsif (Five="1" and Ten="1") then

state_next<=statedone;

end if;

when statedone=>

state_next<=idle;

end case;

end process;

process (state_reg)

begin

Ten_Deposited<="0";

Five_Deposited<="0";

case state_reg is

when idle=>

Ten_Deposited<="0";

Five_Deposited<="0";

done<="0";

when statefive=>

Five_Deposited<="1";

when stateten=>

Ten_Deposited<="1";

Done<="0";

when statedone=>

Ten_Deposited<="1";

Five_Deposited<="1";

done<="1";

end case;

end process;

04-23-2013 05:03 PM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

Hello NapDynamite,

From your other post we were able to make it work but using combinatory logic (no clock signal in VHDL code). Since we don’t directly support VHDL, there is not much we can help you. If there is any VHDL guru here that can check your code, it would be great.

Daniel REDS

RF Systems Engineer

Help us grow.

If a post solves your question, mark it as The Solution.

If a post helps, give Kudos to it.

05-05-2013 09:13 PM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

And I did it! ![]()

05-06-2013 10:58 AM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

Awesome! I'm glad to hear that. Would you mind posting your code and some relevant notes? This will be very useful for the next person who faces these difficulties. Yey productivity!

Daniel REDS

RF Systems Engineer

Help us grow.

If a post solves your question, mark it as The Solution.

If a post helps, give Kudos to it.

05-07-2013 10:48 AM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

Sure 🙂

Here you go

05-07-2013 11:04 AM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

Thanks, NapDynamite. However, you just included your Project (not the actual VI) on the attachment. A good way to include all of the dependencies is to create a source distribution (LLB).

- Right-click on Build Specifications, select New»Source Distribution

- Under Distribution Settings, select Custom as your Packaging Option

- Check the Destination is LLB box and click OK on the warning.

- Choose the Destination Path where you would like the LLB to be saved

- Click Build to create the LLB, or click OK to save the Build Specifications.

Daniel REDS

RF Systems Engineer

Help us grow.

If a post solves your question, mark it as The Solution.

If a post helps, give Kudos to it.

05-07-2013 12:08 PM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

Here you go.

06-17-2013 07:47 AM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

Dear REDS,

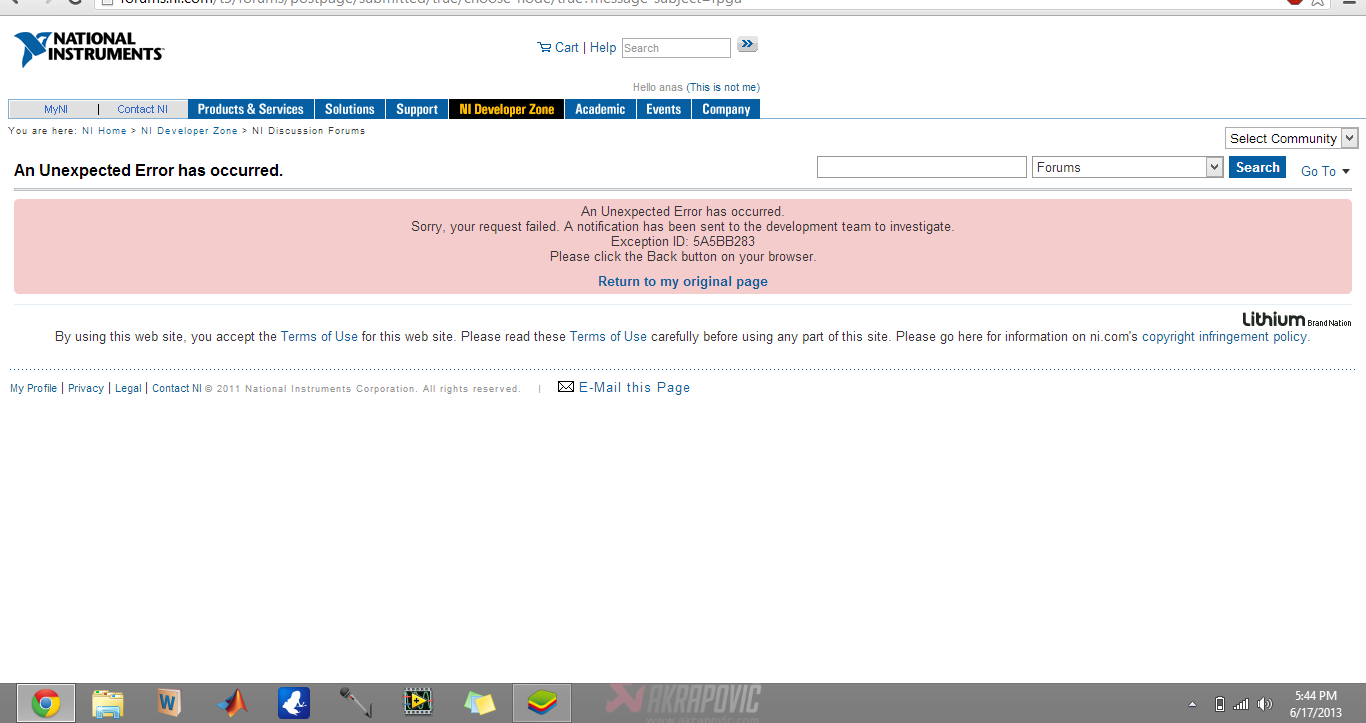

I'm facing this terrible issue of posting any question to any discussion board over here. When I hit the POST button i get an error as shown below.

I mailed to NI but haven't got any reply yet. I just could not find any other way to share this issue. I need help

06-17-2013 10:05 AM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

Hello NapDynamite,

That is a strange behavior I haven’t seen before. Have you tried logging in, logging out and logging back in again? Maybe also try using another web browser, like Internet Explorer or Firefox.

I will ping the department in charge of this on our end so that they can help you.

Daniel REDS

RF Systems Engineer

Help us grow.

If a post solves your question, mark it as The Solution.

If a post helps, give Kudos to it.

06-17-2013 11:25 AM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

I tried everything but nothing seems to work. I have also mailed NI but no response from there. It has been a week now and I'm unable to ask questions which I've got in bulk. Your help will be much, much appreciated.

Regards.