- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

Generate sinusoidal waveform using feedback loop control based on NI FlexRIO (NI 7972 FPGA target, NI 5783 adapter)

08-14-2017 01:55 PM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

Please Open the NI example of "Getting started with NI 5783" first.

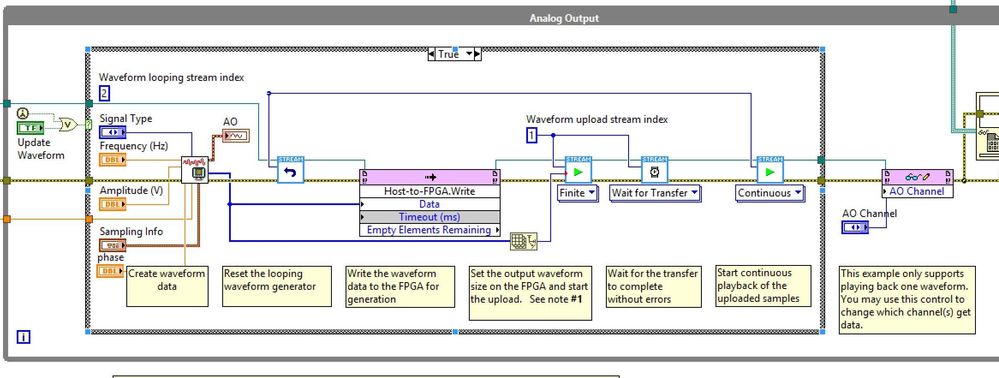

In this example host VI, look at the analog output loop, you will see there is a case structure used to generate sine output signal. In the true case, you give control to the signal's amplitude, frequency, and phase.

Figure 1. true case structure

In the fault case, there are no functions in the case, that means if the case is fault, we just keep the true case parameter in memory without any change and use it.

Figure 2. Original fault case structure

It works well. I can generate a sine signal successfully. But for my system, now I need to make it as a closed loop system.

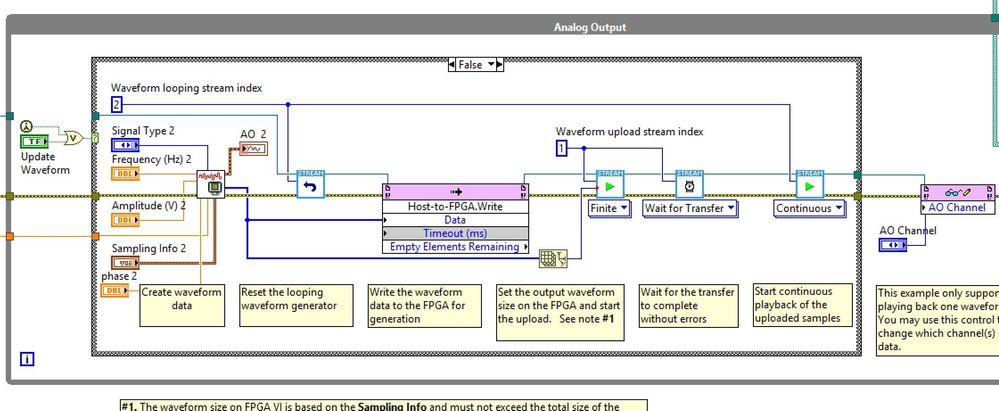

The basic idea is I directly wired AO of NI 5783 to the AI of it (Let's just assume the cable is my plant). On the AI side, using CORDIC method, I can calculate the amplitude and phase of the feedback signal, and then I use a PID controller to control the amplitude and phase, after that, I want to use the feedback amplitude and phase value being controlled to be the new setpoint for the amplitude and phase control of 'create waveform.vi'. That is to say, the setpoints are always changing every single loop. As a result, for the 'fault case', the change I made will be copying all the code in the true case and make the controlled feedback value to be the new phase and amplitude setpoint.

In the fault case, ensuring the setpoints can be updated every single loop, instead of using the real feedback value, as simulation, I use control values to be new setpoints for amplitude and phase to see if my thought works well using FlexRIO:

Figure 3. Modified Fault case structure

The result is that the AO cannot output a good sinusoidal signal. For example, if I set the frequency to be 25MHZ, the output waveform has a 25MHZ signal, but also with variable frequency harmonics(lower or higher than 25MHZ, close to 25MHZ stronger). So I wonder if it happends because these streaming things and FIFO cannot support the data is updated every cycle...

I have asked person in NI about this, they say this kind of FIFO structure might not be realizable, they asked me to generate waveform point directly at FPGA side. But using that way, for the reason that I need my FPGA loop to be updated quickly, it's hard to generate points in a single cycle timed loop without timing violations in FPGA VI.

So I want to ask if there is anyway to realize my thought using the FIFO and streaming structure? If not, any other good ideas?

Thank you.

08-14-2017 01:57 PM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

sorry I upload the picture twice

08-15-2017 01:35 PM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

Did the NI employees say why this might not be realizable? And have you attempted to generate waveform points directly on FPGA side?

I have to agree it seems like an alternative approach to doing this could possibly be done in a SCTL. Although it might be a struggle at first with timing issues, it does seem doable.

08-15-2017 02:45 PM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

Hello Sekine,

I'm glad to see reply from you. The NI employee doesn't explain why this is not achievable, maybe because they tried some ways but didn't solve it.

Yes, generate waveform in a FPGA loop seems a way to solve it, but timing problem in SCTL is struggling to me now...

If there is a way to solve it based on current structure will be best.

Thank you

08-16-2017 12:50 PM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

I am unsure of a direct solution to this based on the current structure given, so I feel like the SCTL might be the best way to go. But then again, I have never done what you are trying to do so there very well may be a way to get this done with this structure.

More specifically, what problems are you struggling with when trying to encompass this within a SCTL?

08-18-2017 05:57 PM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

Hello,

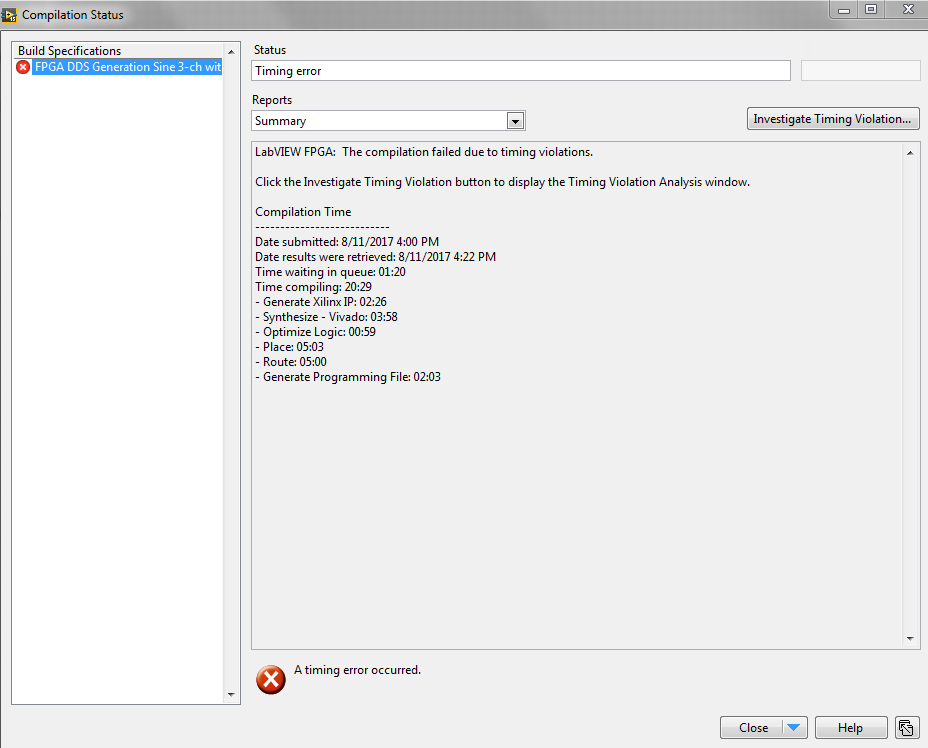

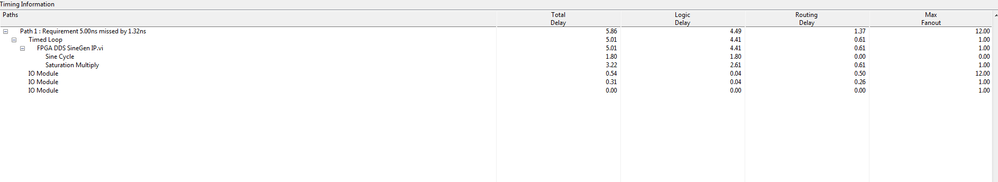

The struggling is when I put waveform generation code in to FPGA VI SCTL, the compilation fails. It has the timing error.

you can see that the timing information shows the requirement for the SCTL is 5ns, that means 200MHZ. However, my data clock is 100MHZ now, so it does not make sense.

Thank you

08-18-2017 06:01 PM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

I don't know why my reply only shows one screenshot, if you click my screenshot, there are three of them.

Thank you

08-21-2017

11:57 AM

- last edited on

10-08-2025

11:26 AM

by

![]() Content Cleaner

Content Cleaner

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

Try pipeling your design so that you don't have to fit everything into a single cycle. The High Performance Developers Guide provides some guidance on how to do this.

The section that starts on page 27 titled "PIPELINING YOUR DESIGN" is where you'll want to start: https://www.ni.com/en/support/documentation/supplemental/13/the-ni-labview-high-performance-fpga-dev...

The DDS vi alone has a 5ns data path delay. If you open that up and add some pipelining between components you should be able to compile at higher frequencies.

08-21-2017 04:53 PM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

Hello David,

Thanks for replying. I already pipelined the DDS VI and main VI, now the code can be compiled. However, for the "look up table 1D" VI in DDS VI, if you select the interpolation mode, it takes at least two cycles no matter how you pipeline the DDS VI. If you don't choose it to be interpolation mode, my output signal is very bad (only have 4 points).

08-21-2017 05:31 PM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

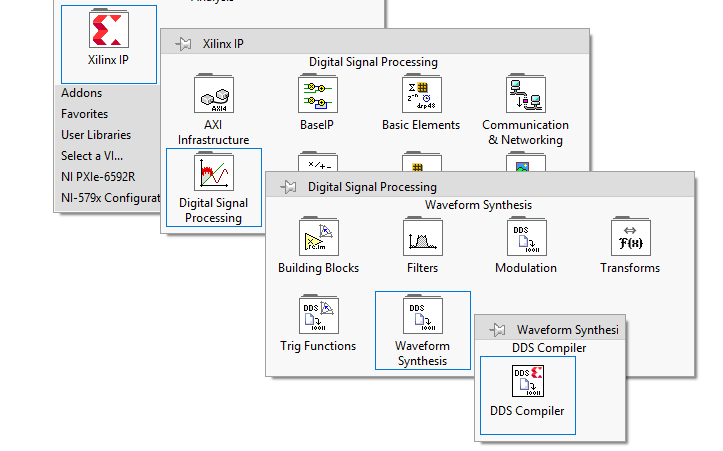

Direct Digital Synthesis has varying levels of complexity depending on what you're trying to do. Rather than work through them yourself, have you considered using the DDS Compiler via the Xilinx IP that is accessible from the functions palette menu in LVFPGA?