ni.com is currently undergoing scheduled maintenance.

Some services may be unavailable at this time. Please contact us for help or try again later.

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

FPGA timed loop

09-09-2015 10:01 AM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

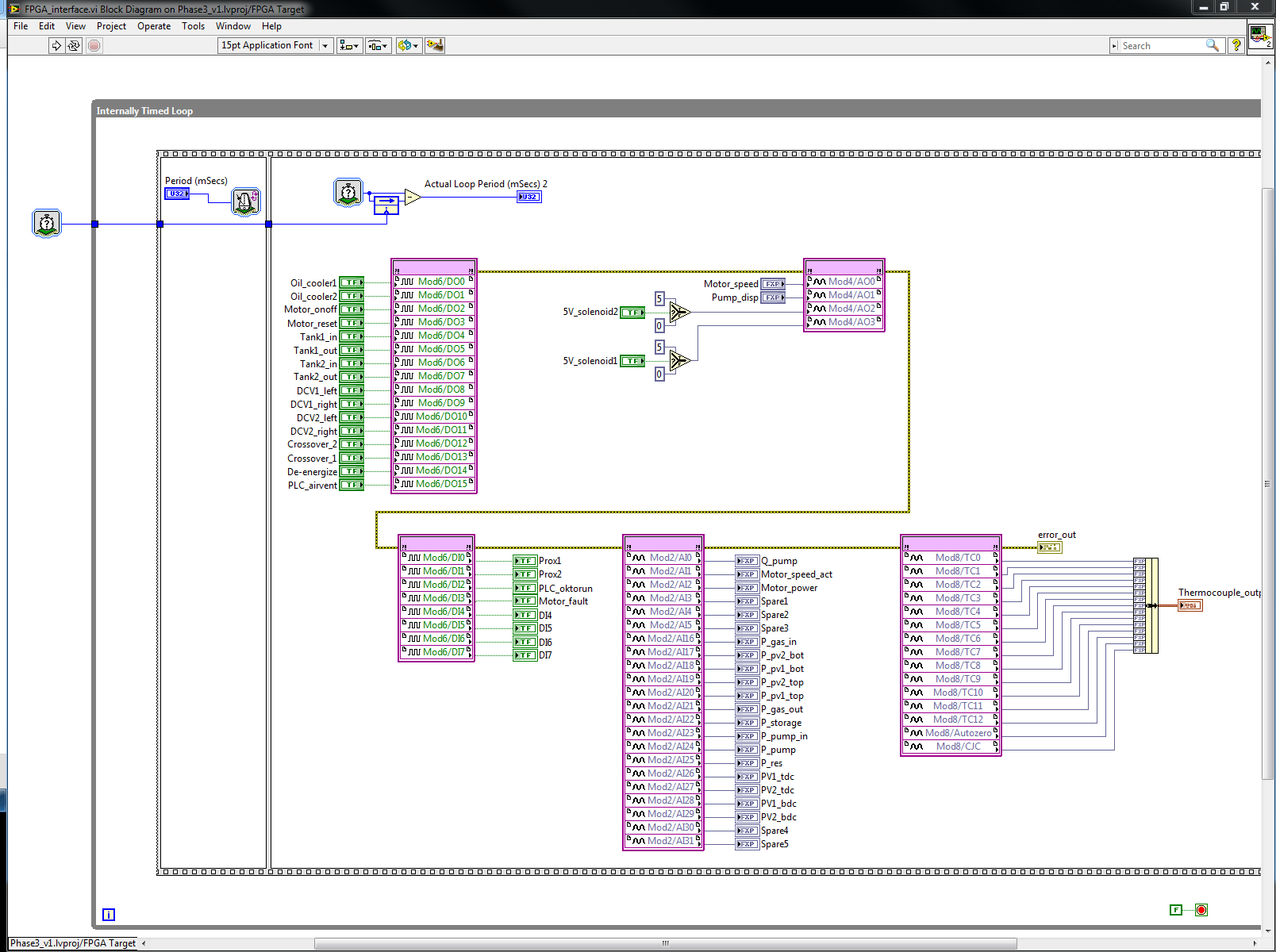

I am trying to do a fixed rate I/O for my FPGA. Dased on examples I implemented the following VI. I set my loop to run at 20 ms, but when I look at the actual loop period, I get 765. Don't understand what I am doing wrong.

If I remove all the I/O, it runs correctly.

09-09-2015 10:27 AM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

Do all of the reading and writing from/to your IO in a single node (ie expand it to include all of the IO you are using here).

There are only two ways to tell somebody thanks: Kudos and Marked Solutions

Unofficial Forum Rules and Guidelines

"Not that we are sufficient in ourselves to claim anything as coming from us, but our sufficiency is from God" - 2 Corinthians 3:5

09-09-2015 10:32 AM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

Thank you. That helped some.

Just figured out the analog acquisition was set to max resolution. If I set it to max speed, I get the desired behaviour. Still the minimum I can get to is 10 ms - which seems pretty slow for an FPGA.

09-09-2015 10:58 AM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

vishalmahulkar wrote: Still the minimum I can get to is 10 ms - which seems pretty slow for an FPGA.

That really depends on the IO modules you are using. Some are faster than others.

There are only two ways to tell somebody thanks: Kudos and Marked Solutions

Unofficial Forum Rules and Guidelines

"Not that we are sufficient in ourselves to claim anything as coming from us, but our sufficiency is from God" - 2 Corinthians 3:5

09-09-2015 03:23 PM - edited 09-09-2015 03:25 PM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

Without looking them up, I expect your thermocouple is the slowest card (they usually are), then analog input.

Try "Merge Errors" after all the I/O is done, instead of serializing the execution by passing errors between them. The FPGA is fantastic at parallelism; use it. Besides, an error in your analog out shouldn't block your analog in from working.

(Typically, I have a loop for each card, so a slow card doesn't hold up anything else. It takes a little more resources for multiple loop delays, but not enough to matter. The down side is that an error just freezes a group of inputs, with little or no explanation unless I add more work.)

[ edit... ] er... I just realized that was what was meant by putting all I/O in a single node. Since that was what you apparently did, I suggest pushing the thermocouple to a separate while loop, and let it be as slow as it wants.

CLD, CPI; User since rev 8.6.

09-09-2015 06:39 PM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

I'd expect the thermocouple module to be the same one used in most applications.

The 9411 will give you old data if you sample it faster than it can get new data so that you can use it in a task/loop with modules that require faster sampling. That shouldn't do much, if anything.

What else is in the loop to the right? What modules do you have and what are their maximum sampling rates? Do you NEED those error wires? They're not nearly as common in FPGA programming as they are in other programming. You said it got better. What are you seeing for a period now?

09-10-2015 07:53 AM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

There is nothing else to the right.

The fastest I can get the loop to execute is 10 ms.

I probably don't need the error wires. Will see if that help any.

Thanks,.

09-10-2015 08:02 AM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

vishalmahulkar wrote:

The fastest I can get the loop to execute is 10 ms.

Considering the fastest thermocouple module I can find is 100S/sec (10ms/sample), I'd say that is about right. If you want your other signals to go faster, then you need to put the thermocouples in a seperate loop.

There are only two ways to tell somebody thanks: Kudos and Marked Solutions

Unofficial Forum Rules and Guidelines

"Not that we are sufficient in ourselves to claim anything as coming from us, but our sufficiency is from God" - 2 Corinthians 3:5