- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

FPGA scan mode COMBINED with FPGA interface mode - C-module 9871

02-25-2016 12:36 PM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

In the past I have developed an application for compact RIO 9063.

chassis was configured to "FPGA mode" and I have written specific code with labview FPGA.

Recently I have added a serial C-module 9871.

Since programing the module in FPGA seems very difficult, I thought (after looking around NI support) to use "scan mode".

However after selection scan mode->deploy all: the FPGA code responds with an error.

So I have rolled back to "FPGA mode" and followed the advice in:

Using the Scan Interface with Individual Modules

(i.e dragged the module to chassis, rather FPGA target)

However is seems NI9871 can not be individually in scan mode.

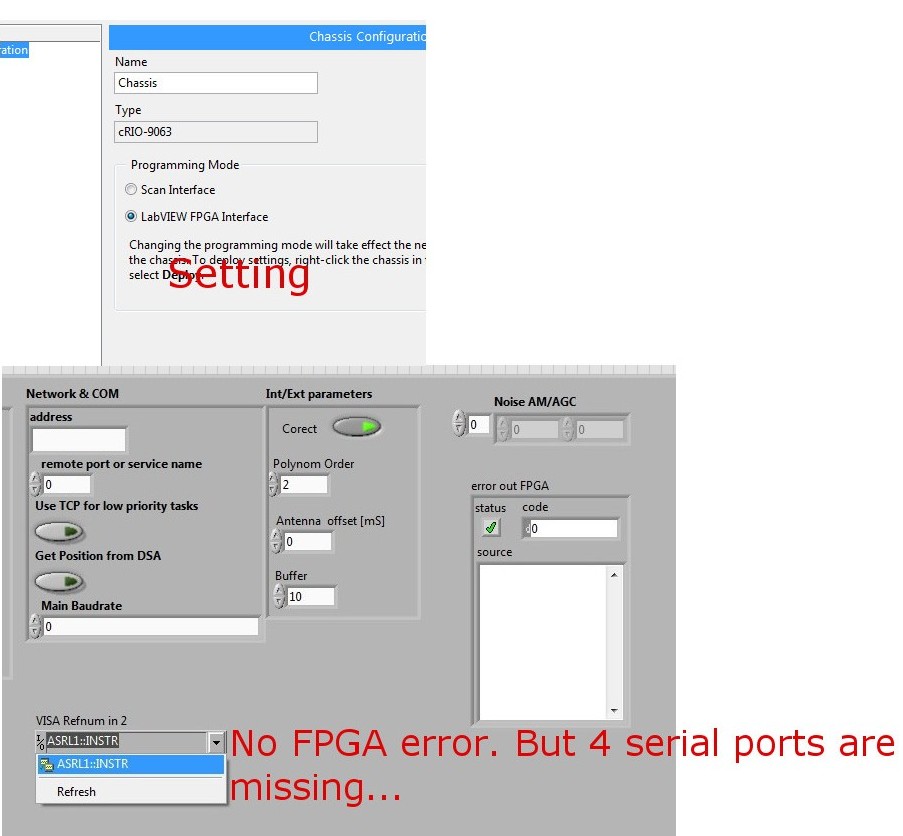

Please see attached screenshots.

Is there a solution?

02-26-2016 10:13 AM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

Hello Hazkel,

Did you also complete the steps to download a compiled bitfile to your project? According to my resources, the 9871 is supported in scan interface mode. According to this help article, the error has to do with automatically closing VISA sessions. Try following the steps detailed there to see if they clear the error. However, I think you need the chassis to be in FPGA Interface mode, as detailed in the help file you linked to.

03-02-2016 09:05 AM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

Thanks for the reply.

the mode of operation I was looking into is called hybrid mode.

The article in the link above is a bit confusing since it is still not clear how to define the chassis.

In the beginning it says define it to "scan interface". but according to the end of the article :"if you get an error - define chassis as FPGA interface"...

Anyway my problem occurred since i did not recompile the FPGA .

I was not aware I had to recompile it since I haven't touched the FPGA code...

As for now it seems my application is working fine.

I have:

1. defined chassis to scan mode

2. recompiled the FPGA code (just open it, and pressed the white arrow)

3. replaced the bitFile in my realtime application.

The only problem I have now:

If I do not close VISA port of the 9871 module - the whlo chassis get idle! The only solution is to have it power cycled...

03-03-2016 04:29 PM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

Hazkel,

After fixing your issue, do you still get the VISA-related error, or can you leave your settings default without your error occuring?

03-04-2016 02:02 AM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

Hi rey,

After the fix apply (i.e recompiling FPGA vi) - i do not get any VISA error. and I am able to communicate with the serial ports.

However, as i mentions previously - if i stop the RT application without closing the VISA port(s) - the whole target get unresponsive. and I need to power cycle the cRIO system.

This may not be such a big of a problem if if I take care to close ports properly. However this is still strange...

Hazkel