ni.com is currently undergoing scheduled maintenance.

Some services may be unavailable at this time. Please contact us for help or try again later.

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

FPGA sample timing and format conversion

Solved!11-14-2020 12:33 PM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

I have a C-RIO with a bunch of cards in it including an NI-9231. I set the sampling rate of the 9231 to 51.2 kS/s, all channels AC coupled, calibration mode "raw." There are two things I don't understand.

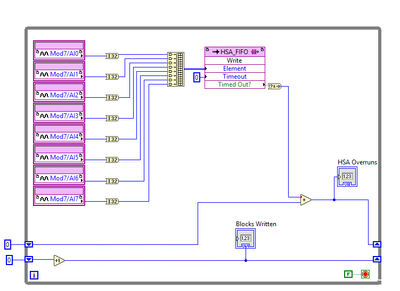

First, about timing: if I set the sampling rate on the NI-9231 configuration, how do I make sure the block below does not run until there are new samples ready? Does that happen automatically, by the I/O nodes not releasing a new sample until one is actually ready?

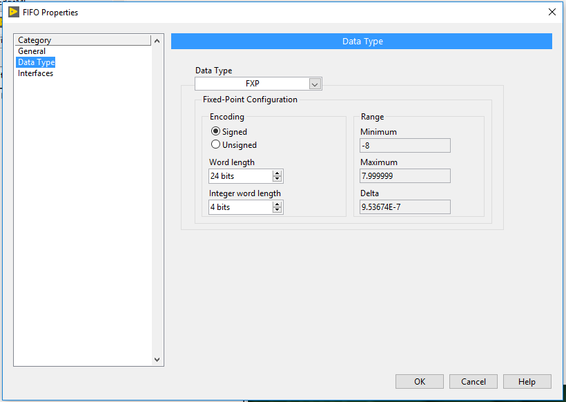

Second: I really want the 24-bit samples as raw. I'm not sure if 'raw' means signed or unsigned. Ultimately I have to get these into a DMA FIFO to get them over to the real-time side of the C-RIO. Do I need to do that conversion to I32? Should it be a U32? What should I expect out of that conversion - will be -2^23-1 to 2^23 sign-extended to 32-bits?

Solved! Go to Solution.

- Tags:

- fpga

11-14-2020 02:38 PM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

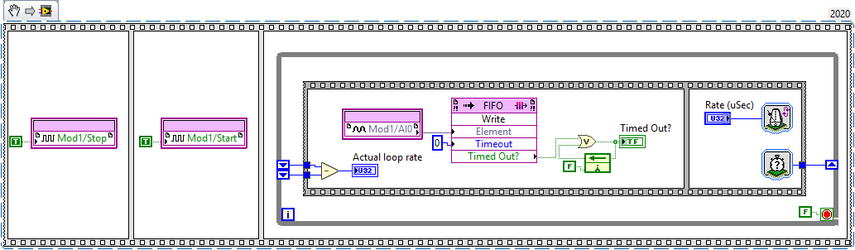

For timing, you can put a dealy into your code that will allow you to control the speed the loop runs at. See the code below for an example.

The NI-9231 is a 24 bit, +/- 5v. To get data out in this format you need to set up your FIFO to take this data. See below, Your word length it 24, your integer word length is 4, that gives you -8 to +8, a range that will fit all your data. Also, it is signed as its + and -.

I hope that helps, Kudos are helpful too!

11-14-2020 04:11 PM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

It's weird, then, that I have no rate limiting at all, but I'm getting data out pretty close to 51,200 writes per second, like it regulates the timing of the loop just because of the setting of the option card. When you do the I/O read are you reading a buffered value? Or is it waiting until a sample is available? To maintain constant time there must be some buffer in the card but I can't find any documentation that tells me how much.

11-14-2020 08:21 PM - edited 11-14-2020 08:22 PM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

My (incomplete) understanding is that the clock that drives the data acquisition is in the NI-9231 module itself. Moreover, I don't believe the module has a buffer, I have also looked for this in the documentation but have not found one. My working theory is that as LabVIEW uses G programming which is a data flow programming, it won't let the "build array" block in your code operate till data is available from the device. The functionality of data-flow programming is what limits the tops speed.

Also, I have never had an issue with my modules returning "old" data, yet another reason I don't believe there is a buffer between the FPGA and the module.